低电阻四刀双掷模拟开关

点击播放视频

This is a modal window.

Beginning of dialog window. Escape will cancel and close the window.

End of dialog window.

This is a modal window. This modal can be closed by pressing the Escape key or activating the close button.

This is a modal window. This modal can be closed by pressing the Escape key or activating the close button.

This is a modal window.

Beginning of dialog window. Escape will cancel and close the window.

End of dialog window.

This is a modal window. This modal can be closed by pressing the Escape key or activating the close button.

This is a modal window. This modal can be closed by pressing the Escape key or activating the close button.

This is a modal window.

Beginning of dialog window. Escape will cancel and close the window.

End of dialog window.

This is a modal window. This modal can be closed by pressing the Escape key or activating the close button.

This is a modal window. This modal can be closed by pressing the Escape key or activating the close button.

This is a modal window.

Beginning of dialog window. Escape will cancel and close the window.

End of dialog window.

This is a modal window. This modal can be closed by pressing the Escape key or activating the close button.

This is a modal window. This modal can be closed by pressing the Escape key or activating the close button.

This is a modal window.

Beginning of dialog window. Escape will cancel and close the window.

End of dialog window.

This is a modal window. This modal can be closed by pressing the Escape key or activating the close button.

This is a modal window. This modal can be closed by pressing the Escape key or activating the close button.

This is a modal window.

Beginning of dialog window. Escape will cancel and close the window.

End of dialog window.

This is a modal window. This modal can be closed by pressing the Escape key or activating the close button.

This is a modal window. This modal can be closed by pressing the Escape key or activating the close button.

低压转换16位I²C总线/SMBus I/O扩展器

适用于开漏和推挽应用的双向电压电平转换器

带有中断的16位I2C总线和SMBus I/O端口

USB PD和Type C限流电源开关

用于充电器和USB-OTG组合应用的双向高端电源开关

双电源转换收发器(开漏,自动方向感测)

| | | | | |

|---|---|---|---|---|---|

| | | | | |

| | | | | |

| | | | | |

| | | | | |

| | | | | |

| | | | | |

| | | | | |

| | | | | |

| | | | | |

| | | | | |

快速参考恩智浦 文档类别.

1-10 / 27 文件

紧凑列表

该选项下未搜到结果。

安全文件正在加载,请稍等

1-10 / 27 文件

紧凑列表

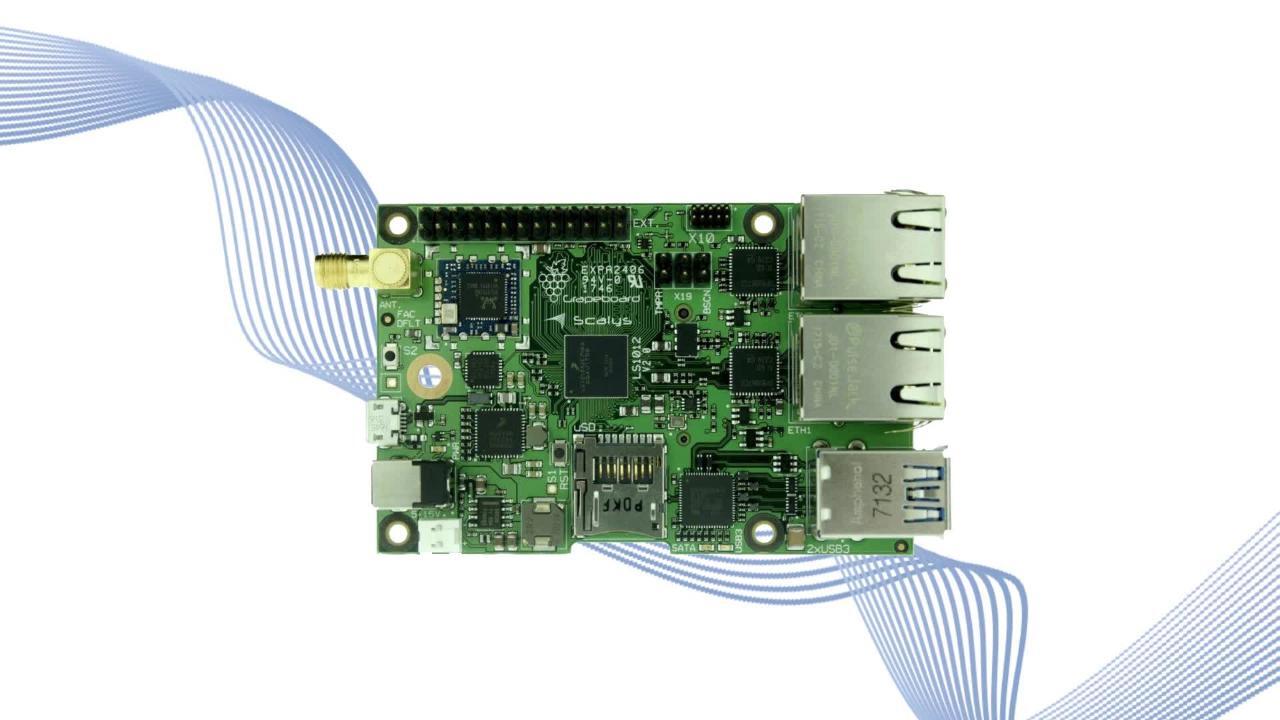

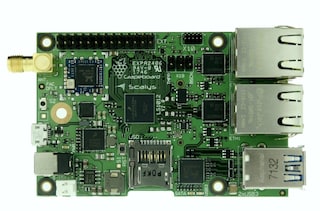

1-5 / 10 硬件

要查找支持该产品的其他合作伙伴产品,请访问我们的 合作伙伴市场.

5 硬件

其他可用硬件. 查看我们的精选合作伙伴解决方案.

快速参考恩智浦 软件类型.

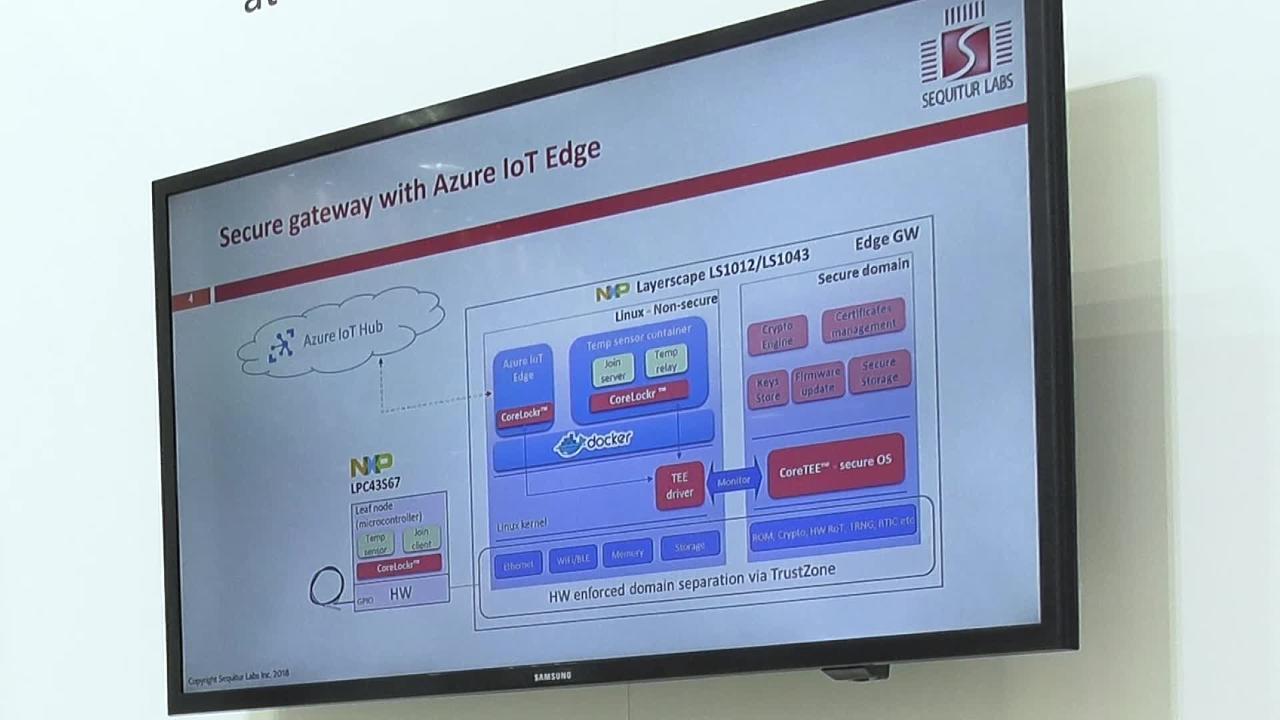

1-5 / 7 软件文件

可访问其他软件。 查看我们的精选合作伙伴解决方案.

注意: 推荐在电脑端下载软件,体验更佳。

安全文件正在加载,请稍等

1-5 / 7 软件文件

可访问其他软件。 查看我们的精选合作伙伴解决方案.

注意: 推荐在电脑端下载软件,体验更佳。

1-5 / 7 工程服务

There are no results for this selection.

There are no results for this selection.

要查找支持该产品的其他合作伙伴产品,请访问我们的 合作伙伴市场.

4 培训

可观看其他培训 查看精选合作伙伴培训.

4 培训

可观看其他培训 查看精选合作伙伴培训.