Layerscape® 1043A和1023A处理器

点击播放视频

This is a modal window.

Beginning of dialog window. Escape will cancel and close the window.

End of dialog window.

This is a modal window. This modal can be closed by pressing the Escape key or activating the close button.

This is a modal window. This modal can be closed by pressing the Escape key or activating the close button.

Layerscape®Access LA9310可编程基带处理器是一款带有集成数据转换器(ADC/DAC)的数字信号处理器,适用于在网络边缘对5G基础设施、DFE和定制通信系统的物理层处理。此处理器成本低、功耗低和可编程信号处理能力强,这些使其成为网络监听、小型无线单元和中继器等应用中价格昂贵FPGA的一个极具吸引力的选择。

ADC/DAC支持射频集成电路的零中频I/Q接口,既适用于6 GHz以下的毫米波应用,也适用于带宽受限的毫米波应用。恩智浦的VSPA DSP实现了数字域中的样本级基带处理,支持灵活的软件定义无线设备。

ADC/DAC模拟子系统支持面向RFIC的零中频I/Q接口,采样速率高达153M Sa/s,适用于低于6 GHz和带宽有限的毫米波应用。矢量信号处理加速器(VSPA)DSP利用恩智浦提供的软件库在数字域中高效地实施采样级基带处理(即数字上/下转换、数字滤波等),实现灵活的软件定义无线设备的标准和专有协议。这些结果通过1个Gen3 PCIe接口提供给主机,通常是LS1023A或LS1043A。该设备包括DMA引擎、时序块和射频控制接口,如I²C、SPI和专有LLCP信令。

此外,LA9310还用于工业和测量用例。对于此类应用,LA9310可作为主机处理器的备用加速器,如i.MX系列设备,也可作为信号预处理器,包括模拟采样采集和初始DSP(滤波器/数据缩减)处理,或作为数学加速器。在这些用例中,备用加速器通常会取代FPGA,通过PCIe或以太网连接。

恩智浦为LA9310提供板级支持包(BSP),其中包括用于所有芯片功能的驱动程序,执行设备完整数据通路的hello-world应用程序示例、VSPA库和在M4内核上运行的FreeRTOS。目标应用的参考代码可用。

CodeWarrior for VSPA使用户能够编译和调试VSPA代码。

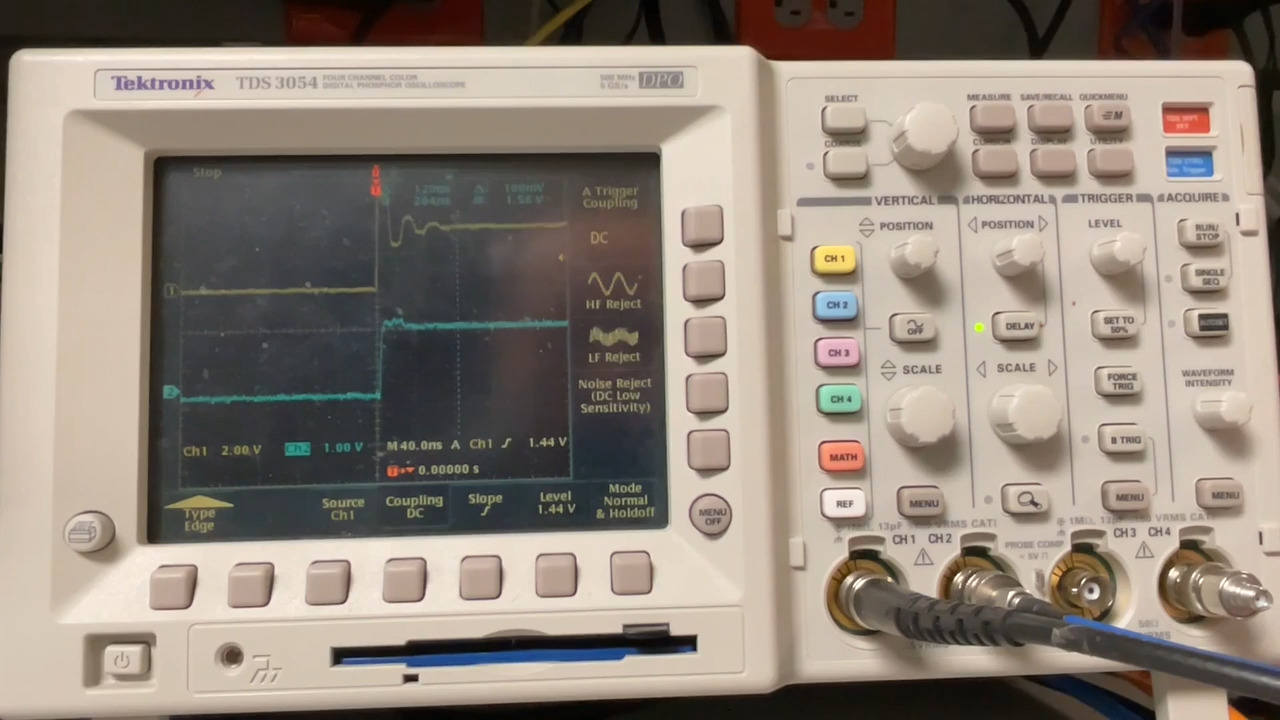

LA9310参考设计套件是一个独立系统,由插入LS1043A参考设计板的LA9310子卡组成。客户可以复制它的设计,用它来评估性能,并用它来调试自己的硬件。

2 结果

包含 0 不推荐用于新设计

部件 | 订购 | 计算机辅助设计模型 | Silicon Rev | 系列 | 状态 | 开发工具 | 认证级别 | 预算报价(不含税) | 封装端接数 | 封装类型 | Package Pitch (mm) | 内核类型 | 内核:内核数量(规范值) | 运行频率[最高](MHz) | Typical Power | L2 Cache (Max) (KB) | SRAM (kB) | SPI | UART | I2C | PCIe | PCIe version | Watchdog timer | 定时器 | 跟踪/调试 | Junction Temperature (Min to Max) (℃) |

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

Rev A0 | LS Access | 正常供应 | LA9310RDK | Industrial | — | 157 | LFBGA157 | 0.5 | Arm Cortex-M4 | 1 | 307 | 1 | 0 | 66 | 1 | 1 | 1 | 1 | PCIe 3.0 | Y | 1 | JTAG | 0 to 105 | |||

Rev A0 | LS Access | 正常供应 | LA9310RDK | Industrial | 100 @ CNY137.78 | 157 | LFBGA157 | 0.5 | Arm Cortex-M4 | 1 | 307 | 1 | 0 | 66 | 1 | 1 | 1 | 1 | PCIe 3.0 | Y | 1 | JTAG | 0 to 105 |

快速参考恩智浦 文档类别.

6 文件

紧凑列表

该选项下未搜到结果。

安全文件正在加载,请稍等

6 文件

紧凑列表

1 硬件产品

要查找支持该产品的其他合作伙伴产品,请访问我们的 合作伙伴市场.

1-5 / 5 工程服务

There are no results for this selection.

There are no results for this selection.

要查找支持该产品的其他合作伙伴产品,请访问我们的 合作伙伴市场.