USB PD和Type C限流电源开关

点击播放视频

This is a modal window.

Beginning of dialog window. Escape will cancel and close the window.

End of dialog window.

This is a modal window. This modal can be closed by pressing the Escape key or activating the close button.

This is a modal window. This modal can be closed by pressing the Escape key or activating the close button.

This is a modal window.

Beginning of dialog window. Escape will cancel and close the window.

End of dialog window.

This is a modal window. This modal can be closed by pressing the Escape key or activating the close button.

This is a modal window. This modal can be closed by pressing the Escape key or activating the close button.

This is a modal window.

Beginning of dialog window. Escape will cancel and close the window.

End of dialog window.

This is a modal window. This modal can be closed by pressing the Escape key or activating the close button.

This is a modal window. This modal can be closed by pressing the Escape key or activating the close button.

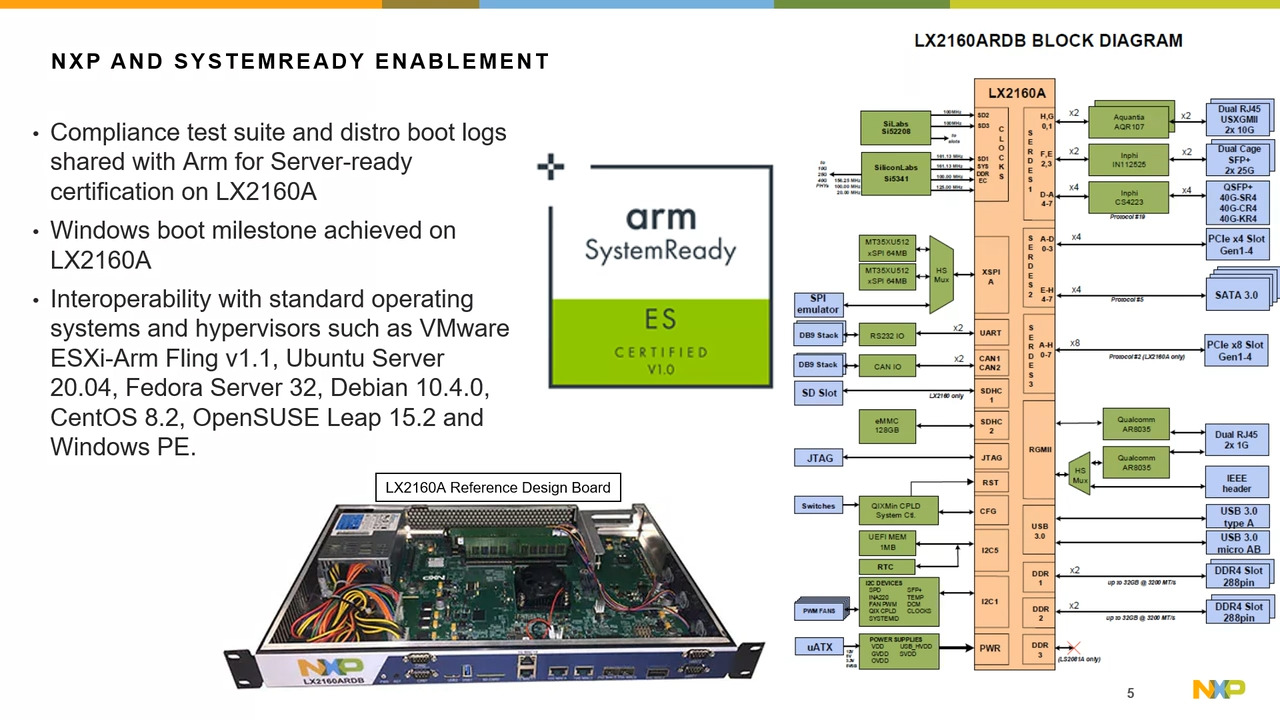

LX2160A多核处理器是Layerscape系列中性能最高的成员,它结合了低功耗的FinFET工艺技术、16个Arm® Cortex®-A72内核以及针对L2/3包处理、安全分流、强大的流量管理和服务质量优化的数据通路加速。

这款先进的16核64位Arm处理器非常适合5G数据包处理、网络功能虚拟化(NFV)、白盒交换、高处理工业计算机、机器学习和智能网络接口卡等应用。高集成度带来了显著的性能优势,例如100GbE、硬件L2交换、具有100Gbps解压/压缩和50Gbps SEC的DPAA2,以及多个PCIe Gen3.0和SATA控制器。

对于边缘计算,该处理器具有强大的数据包分流功能和以太网控制器,可提供出色的计算性能。在一台设备中,您可以进行高端、高速通信,并使用低速外设(例如传感器),并具有处理所有接收到的信息并对其采取行动的计算能力。

Layerscape处理器是恩智浦EdgeVerse™边缘计算平台的一部分。

| LX2160A | LX2120A | LX2080A | |

|---|---|---|---|

| 内核 | 16 | 12 | 8 |

| L2缓存 | 8MB | 6MB | 8MB |

| SerDes | 24 | ||

| PCIe | 多达6个Gen3 | ||

| DDR | 两个DDR4,3200MT/s,256GB容量 | ||

| Plat缓存+PEB | 10MB | ||

| WRIOP | 16个同时存在的MAC;高达16x1GE、10x1/2.5/10GE、6x25GE或2x40/50/100GE的组合;L2交换高达114Gbps | ||

| SEC | 高达50Gbps | ||

| DCE | 高达100Gbps | ||

| 封装 | 40x40mm,1517个引脚 | ||

USB PD和Type C限流电源开关

QorIQ® Layerscape 2088A和2048A多核通信处理器

| | | | | |

|---|---|---|---|---|---|

| | | | | |

| | | | | |

| | | | | |

| | | | | |

| | | | | |

| | | | | |

| | | | | |

| | | | | |

| | | | | |

| | | | | |

LX2160A快速参考恩智浦 文档类别.

1-10 / 34 文件

紧凑列表

该选项下未搜到结果。

安全文件正在加载,请稍等

1-10 / 34 文件

紧凑列表

1-5 / 22 硬件

要查找支持该产品的其他合作伙伴产品,请访问我们的 合作伙伴市场.

快速参考恩智浦 软件类型.

1-5 / 6 软件文件

可访问其他软件。 查看我们的精选合作伙伴解决方案.

注意: 推荐在电脑端下载软件,体验更佳。

安全文件正在加载,请稍等

1-5 / 6 软件文件

可访问其他软件。 查看我们的精选合作伙伴解决方案.

注意: 推荐在电脑端下载软件,体验更佳。

1-5 / 8 工程服务

There are no results for this selection.

There are no results for this selection.

要查找支持该产品的其他合作伙伴产品,请访问我们的 合作伙伴市场.

5 培训

可观看其他培训 查看精选合作伙伴培训.

5 培训

可观看其他培训 查看精选合作伙伴培训.

There are no recently viewed products to display.

查看或编辑浏览历史