低电阻四刀双掷模拟开关

点击播放视频

This is a modal window.

Beginning of dialog window. Escape will cancel and close the window.

End of dialog window.

This is a modal window. This modal can be closed by pressing the Escape key or activating the close button.

This is a modal window. This modal can be closed by pressing the Escape key or activating the close button.

This is a modal window.

Beginning of dialog window. Escape will cancel and close the window.

End of dialog window.

This is a modal window. This modal can be closed by pressing the Escape key or activating the close button.

This is a modal window. This modal can be closed by pressing the Escape key or activating the close button.

QorIQ® T1040四核和T1020双核通信处理器可支持两个或4个集成式64位e5500 Power Architecture®处理器内核,提供网络和通信所需的高性能数据通路加速架构(DPAA)和网络外设接口。

T1040和T1020是业界首款集成了千兆以太网交换机的64位嵌入式处理器。T系列适用于混合控制和数据平台应用,如固定路由器、交换机、嵌入式接入设备、防火墙和其他数据包过滤应用,以及通用嵌入式计算。它具备较高的集成度,可提供卓越的性能优势,简化硬件和软件设计。

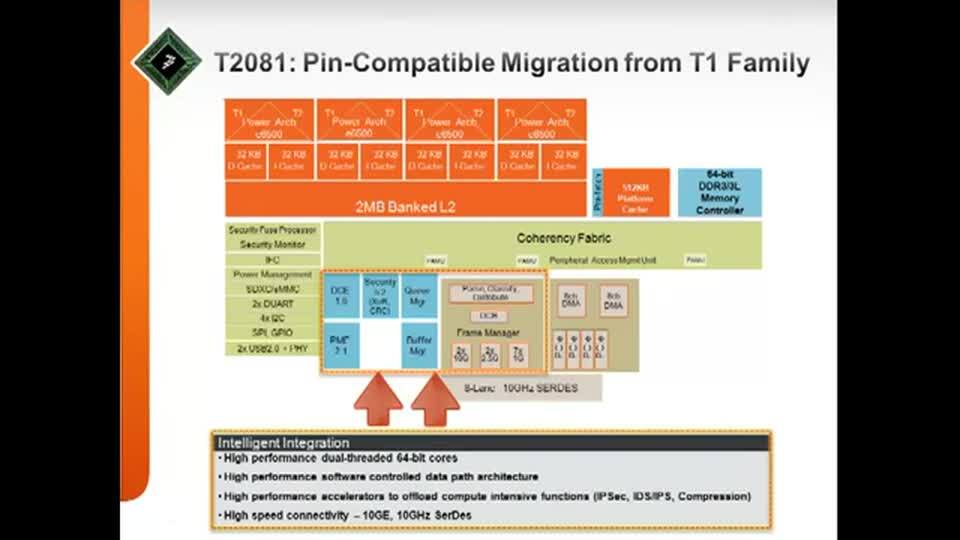

T1系列器件是业界最具可扩展性和引脚兼容性的通信处理器之一 – 为向更高性能的QorIQ T2081器件迁移提供了一条引脚兼容的途径。

| T1020 | T1022 | T1040 | T1042 | T2081 | |

|---|---|---|---|---|---|

| CPU | 2 e5500 | 2 e5500 | 4 e5500 | 4 e5500 | 4 e6500 (dual-threaded) |

| Core Frequency | 1200-1400MHz | 1200-1400MHz | 1200-1400MHz | 1200-1400MHz | 1500-1800MHz |

| DDR I/F | 1x DDR3L/4 to 1600MT/s | 1x DDR3L/4 to 1600MT/s | 1x DDR3L/4 to 1600MT/s | 1x DDR3L/4 to 1600MT/s | 1x DDR3/3L to 2133MT/s |

| Ethernet (with IEEE1588v2) | 8-Port GE Switch + 4x 1GE | 5x 1GE | 8-Port GE Switch + 4x 1GE | 5x 1GE | 2x 1/10GE + 6x 1GE |

| SERDES | 8 lanes (5GHz) | 8 lanes (5GHz) | 8 lanes (5GHz) | 8 lanes (5GHz) | 8 lanes (10GHz) |

| Package | Pin Compatible | ||||

| F104S8A | F104X8A | |

|---|---|---|

| Description | QSGMII PHY Standard Temperature | QSGMII PHY Extended Temperature |

| Operating Temperature (°C) | 0 - 125 | -40 - 125 |

| Package Type | 12x12, QFN, 138-pin, 0.65mm pin pitch | 12x12, QFN, 138-pin, 0.65mm pin pitch |

| Read More | Product Detail | |

适用于开漏和推挽应用的双向电压电平转换器

带有中断的16位I2C总线和SMBus I/O端口

USB PD和Type C限流电源开关

用于充电器和USB-OTG组合应用的双向高端电源开关

1-10 / 16 结果

包含 0 不推荐用于新设计

部件 | 订购 | 计算机辅助设计模型 | 状态 | 预算报价(不含税) | 封装类型 | 封装端接数 | 内核:内核数量(规范值) | 内核类型 | 运行频率[最高](MHz) | Junction Temperature (Min to Max) (℃) | L2 Cache (Max) (KB) | 以太网类型 | PCIe | 支持外部存储器 | Typical Power |

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

正常供应 | 100 @ CNY532.90 | FBGA780 | 780 | 2 | e5500 | 1200 | 0 to 105 | 256 | 10/100 BaseT, 1G, 2.5G | 4 | DDR3L SDRAM, DDR4 SDRAM | 5 | |||

正常供应 | 100 @ CNY639.52 | FBGA780 | 780 | 2 | e5500 | 1400 | 0 to 105 | 256 | 10/100 BaseT, 1G, 2.5G | 4 | DDR3L SDRAM, DDR4 SDRAM | 5 | |||

正常供应 | 100 @ CNY639.52 | FBGA780 | 780 | 2 | e5500 | 1500 | 0 to 105 | 256 | 10/100 BaseT, 1G, 2.5G | — | DDR3L SDRAM, DDR4 SDRAM | 5 | |||

正常供应 | 100 @ CNY507.63 | FBGA780 | 780 | 2 | e5500 | 1200 | 0 to 105 | 256 | 10/100 BaseT, 1G, 2.5G | — | DDR3L SDRAM, DDR4 SDRAM | 5 | |||

正常供应 | 100 @ CNY609.15 | FBGA780 | 780 | 2 | e5500 | 1400 | 0 to 105 | 256 | 10/100 BaseT, 1G, 2.5G | — | DDR3L SDRAM, DDR4 SDRAM | 5 | |||

正常供应 | 100 @ CNY609.15 | FBGA780 | 780 | 2 | e5500 | 1500 | 0 to 105 | 256 | 10/100 BaseT, 1G, 2.5G | — | DDR3L SDRAM, DDR4 SDRAM | 5 | |||

正常供应 | 100 @ CNY612.81 | FBGA780 | 780 | 2 | e5500 | 1200 | -40 to 105 | 256 | 10/100 BaseT, 1G, 2.5G | 4 | DDR3L SDRAM, DDR4 SDRAM | 5 | |||

正常供应 | 100 @ CNY592.35 | FBGA780 | 780 | 4 | e5500 | 1200 | 0 to 105 | 256 | 10/100 BaseT, 1G, 2.5G | — | DDR3L SDRAM, DDR4 SDRAM | 6 | |||

正常供应 | 100 @ CNY710.75 | FBGA780 | 780 | 4 | e5500 | 1400 | 0 to 105 | 256 | 10/100 BaseT, 1G, 2.5G | — | DDR3L SDRAM, DDR4 SDRAM | 6 | |||

正常供应 | 100 @ CNY710.75 | FBGA780 | 780 | 4 | e5500 | 1500 | 0 to 105 | 256 | 10/100 BaseT, 1G, 2.5G | — | DDR3L SDRAM, DDR4 SDRAM | 4 |

T1040快速参考恩智浦 文档类别.

1-10 / 28 文件

紧凑列表

该选项下未搜到结果。

安全文件正在加载,请稍等

1-10 / 28 文件

紧凑列表

1-5 / 7 硬件

.png?imwidth=300)

.png?imwidth=300)

要查找支持该产品的其他合作伙伴产品,请访问我们的 合作伙伴市场.

快速参考恩智浦 软件类型.

3 软件文件

注意: 推荐在电脑端下载软件,体验更佳。

安全文件正在加载,请稍等

3 软件文件

注意: 推荐在电脑端下载软件,体验更佳。

3 工程服务

There are no results for this selection.

There are no results for this selection.

要查找支持该产品的其他合作伙伴产品,请访问我们的 合作伙伴市场.

There are no recently viewed products to display.

查看或编辑浏览历史