跳转至

开箱即用

1.1 评估板介绍

1.2 处理器模块介绍

获取软件

2.1 安装控制台Tera Term

Tera Term是支持UTF-8协议的免费开源软件终端仿真器。现在TTSSH支持SSH2协议(最初版本支持SSH1)。

Tera Term目前是Tera Term Pro 2.3,是后续版本。获得了原作者的正式认可。

2.2 安装FTDI CDM WHQL驱动程序

FTDI芯片的FTDI CDM v2.12.28 WHQL串行配置驱动程序

下载FTDI CDM驱动程序2.3 安装Win32 Disk Imager

这是一款Windows工具,用于将镜像写入USB记忆棒或SD/CF卡。

下载Win32 Disk Imager2.4 安装Packet Sender应用

这是一个免费的实用程序,用于发送和接收网络数据包:TCP、UDP和SSL。

下载Packet Sender连接

让我们开始试用它。

3.1 安装S32G插槽和散热器

| 1 | 带Ironwood Electronics SG-BGA-6124插槽的S32G-PROCEVB3-S:S32G处理器模块 |

| 2 | M4159散热器 |

| 3 | 六角扳手 |

| 4 | Timiy真空吸笔工具 |

观看视频,了解如何安装插槽和散热器。您还可以使用分步指南。

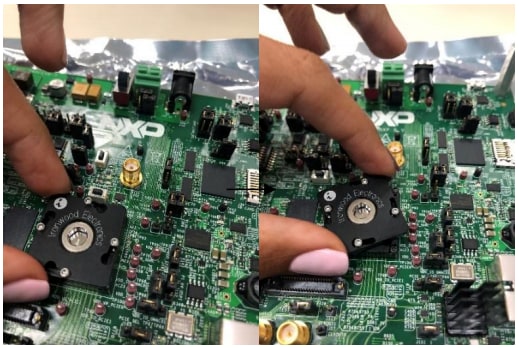

1. 向左旋转内六角螺丝,松开插槽顶部。

2. 向左转动并向上提起插槽盖,取下插槽盖。将其放到一边。

3. 使用真空工具取下并从插槽中卸下压板。将其放到一边。

4. 使用真空工具,取下S32G并将其放在插槽底座中。

注:确保极性标记与通过点指示的插槽极性标记匹配。

5. 用六角扳手从插槽盖上完全卸下螺丝。

6. 使用真空工具将压板安装在S32G设备顶部

7. 装回插槽盖并向右旋转,锁定到位

8. 顺时针缓慢旋转散热器,直到与压板初次接触。转动1/4圈,充分接触。切勿对插槽施加过大压力。

注意:切勿用力推动散热器。

安装完成后,应如图中所示:

3.2 连接12 V电源

当将S32G-PROCEVB3-S栈叠在S32GRV-PLATEVB上时

:S32G-PROCEVB3-S上的跳线J96 ,应在位置1-2,只需要为S32GRVPLATEVB通电。

将电源连接至S32GRV-PLATEVB上的12 V电源插孔P3。

单独使用S32G-PROCEVB3-S时:

跳线J96应在位置2-3上。

将电源连接至S32G-PROCEVB3-S上的12 V电源插孔P1。

运行

4.1 设置Tera Term 4控制台

1. 打开Windows PC上的Tera Term。

2. 选择S32G-PROCEVB3-S的微型USB J58所连接的串行端口,点击OK (确定)。

3. 前往Setup > Serial Port,选择115200波特率

4.2 为S32G-VNP-EVB3通电

打开S32GRV-PLATEVB上的电源开关 SW1 ,以及S32G-PROCEVB3-S上的电源开关 SW10 。

4.3 运行诊断

诊断实用程序自动从SD卡执行。

Tera Term上的控制台显示屏显示诊断测试的状态。

SD卡镜像日志

我们提供带S32G-VNP-EVB3和S32G-VNP-EVB3映像的现成SD卡,帮助人们开始使用并记录数据

Diagnostic Tests: build time = Nov 9 2021 17:28:48 CPU: NXP S32G399A rev. 1.0 Board: S32G-VNP-EVB3 Core: CM7_0 MC_CGM_0 Clock Mux 0 -> XBAR_CLK (Core Clock) CORE_DFS_1 Clock -> MC_CGM_0 Clock Mux 0 CORE_VCO Clock -> CORE_DFS_1 Clock FXOSC -> CORE_VCO Clock FXOSC, as available on S32G-VNP-EVBx: 40000000Hz All further clocks derived from FXOSC value CORE_VCO Clock: 2000000000Hz CORE_DFS Clock: 799999992Hz XBAR_CLK: 399999996Hz Test#1: Setup Init - OK Test#2: Running LINFLEXD Test FXOSC -> PERIPH_PLL_PHI3_CLK MC_CGM_0 Clock Mux 8 -> LIN_CLK LIN CLK: 80000000Hz LIN 0 Mode: UART UART 0 Mode: 8-Bit Mode UART 0 Baud Rate: 115273bps UART 0 TX_INT: Disabled UART 0 RX_INT: Disabled UART 0 SIUL2 Settings: PK15, PL00 Testing LINFLEX Rx Press enter to continue Test#2: Test OK Test#3: Running Flash Read Test Test#3: Ensure that the QSPI flash has been written before running this test, For further info please refer the user guide PERIPH_DFS1_CLK -> QSPI_CLK PERIPH_VCO -> PERIPH_DFS1_CLK FXOSC -> PERIPH_VCO Test#3: Test OK Test#4: Running STM Test STM CLK = XBAR_CLK STM Instance: 0 STM 0 Channel: 0 STM 0 Ticks: 3855 STM 0 NVIC ID: 24 STM CLK = XBAR_CLK STM Instance: 0 STM 0 Channel: 1 STM 0 Ticks: 3855 STM 0 NVIC ID: 24 STM CLK = XBAR_CLK STM Instance: 0 STM 0 Channel: 2 STM 0 Ticks: 3855 STM 0 NVIC ID: 24 STM CLK = XBAR_CLK STM Instance: 0 STM 0 Channel: 3 STM 0 Ticks: 3855 STM 0 NVIC ID: 24 Test#4: Test OK Test#5: Running PIT Test PIT CLK = XBAR_CLK PIT Instance: 0 PIT 0 Counter: DOWN PIT 0 Timer: 0 PIT 0 NVIC ID: 53 PIT 0 Ticks: 4096 PIT CLK = XBAR_CLK PIT Instance: 0 PIT 0 Counter: DOWN PIT 0 Timer: 1 PIT 0 NVIC ID: 53 PIT 0 Ticks: 4096 PIT CLK = XBAR_CLK PIT Instance: 0 PIT 0 Counter: DOWN PIT 0 Timer: 2 PIT 0 NVIC ID: 53 PIT 0 Ticks: 4096 PIT CLK = XBAR_CLK PIT Instance: 0 PIT 0 Counter: DOWN PIT 0 Timer: 3 PIT 0 NVIC ID: 53 PIT 0 Ticks: 4096 PIT CLK = XBAR_CLK PIT Instance: 0 PIT 0 Counter: DOWN PIT 0 Timer: 4 PIT 0 NVIC ID: 53 PIT 0 Ticks: 4096 PIT CLK = XBAR_CLK PIT Instance: 0 PIT 0 Counter: DOWN PIT 0 Timer: 5 PIT 0 NVIC ID: 53 PIT 0 Ticks: 4096 PIT CLK = XBAR_CLK PIT Instance: 0 PIT 0 Counter: DOWN PIT 0 Timer: 6 PIT 0 NVIC ID: 53 PIT 0 Ticks: 4096 Test#5: Test OK Test#6: Running SWT Test SWT CLK = XBAR_DIV3_CLK SWT Instance: 0 SWT 0 Counter: UP SWT 0 NVIC ID: 14 SWT 0 Time Out Value: 392400 Test#6: Test OK Test#7: Running I2C_0 Test I2C CLK source: XBAR_DIV3_CLK I2C CLK: 166666666Hz I2C 0 Mode: Master I2C Slave Address: 0xA0 Test#7: Test OK Test#8: Running I2C_2 Test I2C CLK source: XBAR_DIV3_CLK I2C CLK: 166666666Hz I2C 2 Mode: Master I2C Slave Address: 0xA2 Test#8: Test OK Test#9: Running I2C_4 Test I2C CLK source: XBAR_DIV3_CLK I2C CLK: 166666666Hz I2C 4 Mode: Master I2C Slave Address: 0x20 Test#9: Test OK Test#10: Running DSPI_5 Test PERIPH_PLL_PHI7_CLK -> DSPI CLK FXOSC -> PERIPH_PLL_PHI7_CLK DSPI 5 Mode: MASTER DSPI 5 Frame Size: 7Byte DSPI 5 CPOL : 0 DSPI 5 CPHA : 1 DSPI 5 connected with RGMII-A Switch SJA1105Q Reading Switch ID Ensure that the PROC board is correctly mounted on the PLAT board Test#10: Check connections as highlighted above Test#11: Running MDIO Test Running MDIO READ Test MAC: GMAC0, PHY HW Address# 0x04, PHY ID: 0x0022 MAC: GMAC0, PHY HW Address# 0x05, PHY ID: 0xFFFF MAC: PFE_MAC1, PHY HW Address# 0x04, PHY ID: 0x0022 MAC: PFE_MAC1, PHY HW Address# 0x05, PHY ID: 0xFFFF MAC: PFE_MAC0, PHY HW Address# 0x02, PHY ID: 0xFFFF MAC: PFE_MAC0, PHY HW Address# 0x03, PHY ID: 0xFFFF MAC: PFE_MAC0, PHY HW Address# 0x06, PHY ID: 0xFFFF MAC: PFE_MAC1, PHY HW Address# 0x01, PHY ID: 0xFFFF MAC: PFE_MAC0, PHY HW Address# 0x08, PHY ID: 0x31C3 MAC: PFE_MAC2, PHY HW Address# 0x02, PHY ID: 0xFFFF MAC: PFE_MAC2, PHY HW Address# 0x03, PHY ID: 0xFFFF MAC: PFE_MAC2, PHY HW Address# 0x06, PHY ID: 0xFFFF MAC: PFE_MAC2, PHY HW Address# 0x08, PHY ID: 0x31C3 Test#12: Running USB HOST Test USB CLK source= XBAR_DIV4_CLK USB Mode: Host No USB device connected Test#12: Check the USB connection to the device and make sure J45 is connected on the PROC board Test#13: Running LLCE CAN Loopback Tests FXOSC -> CAN_PE_CLK FXOSC: 40000000Hz CAN_PE_CLK: 40000000Hz LLCE CAN 1: Set Controller Mode : NOK LLCE CAN 2: Set Controller Mode : NOK LLCE CAN 3: Set Controller Mode : NOK LLCE CAN 4: Set Controller Mode : NOK LLCE CAN 5: Set Controller Mode : NOK LLCE CAN 6: Set Controller Mode : NOK LLCE CAN 7: Set Controller Mode : NOK LLCE CAN 8: Set Controller Mode : NOK LLCE CAN 9: Set Controller Mode : NOK LLCE CAN 10: Set Controller Mode : NOK LLCE CAN 11: Set Controller Mode : NOK LLCE CAN 12: Set Controller Mode : NOK LLCE CAN 13: Set Controller Mode : NOK LLCE CAN 14: Set Controller Mode : NOK LLCE CAN 15: Set Controller Mode : NOK Tx: LLCE CAN 0 & Rx: LLCE CAN 1: Test NOK, Check HW connections Ensure that jumper J155 on PROCEVB is in position: 3-5; 4-6 Tx: LLCE CAN 2 & Rx: LLCE CAN 3: Test NOK, Check HW connections Tx: LLCE CAN 4 & Rx: LLCE CAN 5: Test NOK, Check HW connections Tx: LLCE CAN 6 & Rx: LLCE CAN 7: Test NOK, Check HW connections Tx: LLCE CAN 8 & Rx: LLCE CAN 9: Test NOK, Check HW connections Tx: LLCE CAN 10 & Rx: LLCE CAN 11: Test NOK, Check HW connections Tx: LLCE CAN 12 & Rx: LLCE CAN 13: Test NOK, Check HW connections Tx: LLCE CAN 14 & Rx: LLCE CAN 15: Test NOK, Check HW connections Ensure that jumper J166 on PROCEVB is in position: 3-5; 4-6 Ensure that jumper J167 on PROCEVB is in position: 3-5; 4-6 Test#14: Running LLCE LIN loopback Tests FXOSC -> PERIPH_PLL_PHI3_CLK MC_CGM_0 Clock Mux 8 -> LIN_BAUD_CLK LLCE_LIN_BAUD_CLK = 83333334Hz Master: LLCE LIN 0 & Slave: LLCE LIN 1: Test NOK, Check HW connections Ensure that jumpers J31 and J32 on PLATEVB are in position: 1-2 Master: LLCE LIN 2 & Slave: LLCE LIN 3: Test NOK, Check HW connections Test#15: Running SD Read Test Test#15: Ensure that the SD card is already written, For further info please refer the user guide PERIPH_DFS3_CLK -> USDHC_CLK PERIPH_VCO -> PERIPH_DFS3_CLK FXOSC -> PERIPH_VCO Expected value to be read at offset 0x0: 0xD1010060 Test#15: Test OK Test#16: Running ADC Test Test#16: In case no external voltage is applied on the input channels, random value may be read PERIPH_PLL_PHI1_CLK -> ADC CLK FXOSC -> PERIPH_PLL_PHI1_CLK ADC0_0 value = 614 mV ADC0_1 value = 826 mV ADC0_2 value = 680 mV ADC0_3 value = 923 mV ADC0_6 value = 952 mV ADC0_7 value = 865 mV ADC1_4 value = 786 mV ADC1_5 value = 872 mV ADC1_8 value = 920 mV ADC1_9 value = 1040 mV ADC1_10 value = 872 mV ADC1_11 value = 956 mV Test#17: Running PCIe_CC Test PCIe reference clock= External (100MHz) PCIe Mode: Root Complex PCIe Gen: 1 PCIe Link Width: X1 Waiting for PCIe device to be connected Test#17: Connect x1 PCIe card to PLAT board x16 header Test#18: NMI input is enabled, Press SW16 on EVB and observe LED D15 for the toggle Test#19: Running TMU Test TMU Site 1 immediate temperature measured in Celsius: 40 TMU Site 1 average temperature measured in Celsius: 40 TMU Site 2 immediate temperature measured in Celsius: 40 TMU Site 2 average temperature measured in Celsius: 40 TMU Site 3 immediate temperature measured in Celsius: 42 TMU Site 3 average temperature measured in Celsius: 42 Test#19: Test OK Test#20: Running PFE Test PFE CLK source= ACCEL_PLL_PHI1_CLK PFE_PE_CLK: 600000000Hz PFE MAC: 0 MAC Mode: SGMII MAC Speed: 1G SerDes PHY reference clock: 100Mhz AutoNeg: Disabled Clock source: Internal PFE MAC: 1 MAC Mode: SGMII MAC Speed: 1G SerDes PHY reference clock: 100Mhz AutoNeg: Disabled Clock source: Internal PFE MAC: 2 MAC Mode: RGMII MAC Clock: 125Mhz MAC Speed: 1G Routing Table entries: Total number of routes created : 7 Route 1: Routing Table Base Address 0x345C2480 PFE MAC 1 --> PFE MAC 0 Src IP : 192.168.0.20, Dest IP 192.168.0.21 Src Port : 10, Dest Port : 5 Route 2: Routing Table Base Address 0x345C1B80 PFE MAC 0 --> PFE MAC 0 Src IP : 17.17.17.17, Dest IP 17.17.17.17 Src Port : 5, Dest Port : 10 Route 3: Routing Table Base Address 0x345C2C80 PFE MAC 1 --> PFE MAC 1 Src IP : 34.34.34.34, Dest IP 34.34.34.34 Src Port : 5, Dest Port : 10 Route 4: Routing Table Base Address 0x345C1F00 PFE MAC 0 --> PFE MAC 0 Src IP : 192.168.0.15, Dest IP 192.168.0.15 Src Port : 10, Dest Port : 5 Route 5: Routing Table Base Address 0x345C2000 PFE MAC 1 --> PFE MAC 1 Src IP : 192.168.0.16, Dest IP 192.168.0.16 Src Port : 10, Dest Port : 5 Route 6: Routing Table Base Address 0x345C1E00 PFE MAC 2 --> PFE MAC 2 Src IP : 192.168.0.14, Dest IP 192.168.0.14 Src Port : 10, Dest Port : 5 Route 7: Routing Table Base Address 0x345C2180 PFE MAC 1 --> PFE MAC 0 Src IP : 192.168.0.17, Dest IP 192.168.0.18 Src Port : 10, Dest Port : 5 PFE MAC2: RX Clock not provided Make sure the SJA1105 test is enabled and the PROC board is mounted on the PLAT board PFE MAC0: External device not connected OR incorrect clock provided to SerDes1 PFE MAC1: External device not connected OR incorrect clock provided to SerDes1 Test#20: Check ethernet connections and clock values as highlighted above Test#21: Running LINFLEXD_1 Test For running LinflexD_1 test, do the following changes on PROC EVB3 board Remove jumper from pins 2-3 of J130 and short J186-pin1 to J130-pin2 Change J185 from 1-2 position to J185 2-3 position Make sure an additional micro USB cable is connected b/w J179 on PROC board and PC for console prints over LinFlexD_1 Check logs on serial terminal on PC connected to LinFlexD_1 Test#21: Test NOK Test#22: LPDDR4 Initialization and Test Initializing DDR Step 1: Configuration of enabling partitions starts for DDR system Step 2: Configuration of DDR PLL DDR clock configurations done for 3200MT/s Step 3: Configuration of DDR clock source selection starts ***** ECC Enable ***** ddr_init successful !!! Initialization Succeeded !!! DDR Test : LPDDR4 Tests - Started DDRTest#1:DDR Test - memTestDataBus - Started DDRTest#1:DDR Test - memTestDataBus - Passed !!! DDRTest#2:DDR Test - memTestAddressBus - Started DDRTest#2:DDR Test - memTestAddressBus - Passed !!! DDRTest#4:DDR Test - ddr_row_hop_read_test - Started DDR atrributes and parameters passed into this test: DRAM start address: 0x60000000 Attrib: density is - 256 MB Programming source memory... ... Written bytes = 0x10000000 Write Done, now perform Read .. DDRTest#4: ddr_row_hop_read_test - Passed !!! DDRTest#5:DDR Test - ddr_memcpy_random_data_pattern_test - Started dramStartAddr = 0x60000000 density = 256MB Programming source memory for: Bank 1 . Bank 2 . Bank 3 . Bank 4 . Completed source memory fill, now performing memcpy.... Completed memcpy, now verifying destination: Bank 1 verification . Bank 1 verification complete, now verifying bank 2 . Bank 2 verification complete, now verifying bank 3 . Bank 3 verification complete, now verifying bank 4 . Bank 4 verification complete Memory transfer successful!! DDRTest#5: ddr_memcpy_random_data_pattern_test - Passed !!! DDRTest#6:DDR Performance Monitor Test - ddr_perf_mon_test - Started Performance Numbers: ***** ECC Enabled ******* DRAM access duration for read throughput 5368709 us Performance Monitor - Counter_2 Write Data Count 1324584 Performance Monitor - Counter_1 Read Data Count 24689709 DRAM last read location: 0x63e2f0b4 DRAM Total read locations in total duration: 16301101 Bytes DRAM last write location: 0x678fb038 DRAM Total write locations in total duration: 31714318 Bytes DDRTest#6: ddr_perf_mon_test - Passed !!! Test#22: Test OK All tests complete, Core in While(1) 设计资源

芯片文档

软件

获取帮助

培训

- 使用AWS Connected Mobility解决方案和恩智浦S32G处理器开发先进的车载云服务应用

- 在恩智浦S32G处理器上使用AirbiquityOTAmatic®协调复杂且安全的汽车OTA软件更新和数据管理

- COQOS Hypervisor SDK与S32G处理器携手服务未来网络处理

- DDS及TSN:Connext Drive®软件与恩智浦S32G处理器硬件碰撞出可靠的通信技术

论坛

在专用论坛上,可与其他工程师交流,获取专家建议,了解如何使用S32G汽车网络处理评估板3进行产品设计。