The DSP56303 is intended for use in telecommunication applications, such as multi-line voice/data/fax processing, videoconferencing, audio applications, control, and general digital signal processing.

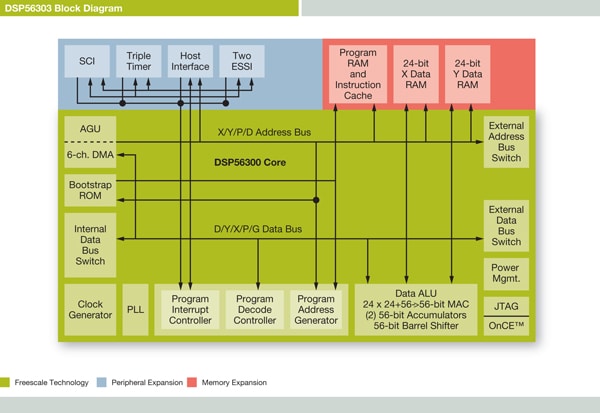

The DSP56303 is a member of the DSP56300 core family of programmable CMOS Digital Signal Processors (DSPs). This family uses a high performance, single clock cycle per instruction engine providing a twofold performance increase over Our popular DSP56000 core family, while retaining code compatibility. Significant architectural enhancements to the DSP56300 core family include a barrel shifter, 24-bit addressing, instruction cache, and DMA. The DSP56303 offers 100 MMACS using an internal 100 MHz clock at 3.0-3.6 volts. The DSP56300 core family offers a new level of performance in speed and power provided by its rich instruction set and low power dissipation, enabling a new generation of wireless, telecommunications, and multimedia products.