Though 2014 was relatively a brief time ago, the advancement of technology

over the last few years has been astounding. Consider the acceleration of

Arm based shipments, which over the last 4 years has doubled. That is an increase of 50 billion

devices which integrate an Arm CPU from 2013 to 2017! Back in 2014, the

super-scalar Arm® Cortex®-M7 processor was unleashed into a market

poised for the age where smart and connected things would proliferate into the

billions. Today, with

8.4 billion connected things

having shipped in 2017, the capabilities of the top tier Arm Cortex-M

processor has already enabled many classes of embedded devices, from wearables

to industrial controllers. Now with broad industry focus on the application of

artificial intelligence, machine learning, vision and voice processing that

require more capable edge computation, the Arm Cortex-M7 and the NXP SoC

platforms which integrate it, are crossover points for the MCU developer to

help achieve the capabilities needed to address emerging requirements.

Central to the compute capability of the SoC is the CPU. Close to the release

of the Arm Cortex-M7, I had the pleasure of collaborating with Arm on a

whitepaper

that explores the processor capabilities in detail. The information there is

arguably more relevant today, so please have a read.

At the time we wrote the whitepaper, little did we know the extent to which

we could achieve with the processing speeds and peripherals that we’ve

done with the new i.MX RT. There is an excellent

whitepaper

that outlines how its attributes make it unclassifiable in the traditional

embedded space. With the i.MX RT family, we have created the new

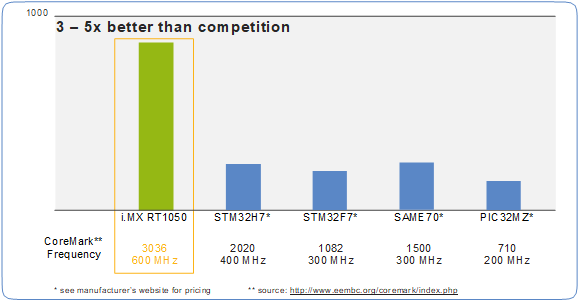

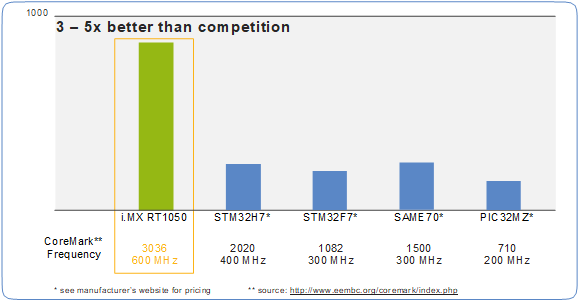

‘crossover processor’ class. One of the benefits of this class

of devices is shown in the below graph which relates performance to the price

of different options in the market.

So, I would like to add the following addendum to the

whitepaper

to explore the Cortex-M7 integration for our i.MX RT crossover processor.

The below diagram captures the architectural details. With regards to cache,

the i.MX RT integrates 32KB for the instruction and 32KB for the data caches.

This is the largest size in the market and ensures that the processor is not

limited by any delays imposed by slower memories. For the Tightly Coupled

Memory (TCM), the i.MX RT has a FlexRAM block of memory. This allows

customization of the TCM up to the largest size available (256KB I-TCM, 256KB

D-TCM). The user can select this maximum size, or repurpose the FlexRAM to

work as On-Chip SRAM.

With regards to the use of AXI on the i.MX RT, there are a broad range of AXI

which are integrated. Some specific peripherals to highlight which are

relevant to emerging trends are the LCD Controller, 2D graphics acceleration

engine, Parallel camera sensor interface and cryptographic accelerator (Data

Co-Processor-DCP). These components differentiate the i.MX RT in the market

and align to the need for the highest compute performance together with

reliable security and assured privacy at the lowest cost possible. Finally,

most relevant to the computational capabilities of the i.MX RT is the

processor speed. Reaching 600MHz allows the RT to be throttled up for the most

intensive calculations.

NXP IoT and Security Solutions team, which applies NXP technology to address market challenges, is focusing on

enhancing the i.MX RT with voice and vision components. For the next 100

billion Arm-enabled chips coming in the next 4 years, I expect many to take

advantage of the capabilities provided by the CPU and the SoCs.

To learn more about i.MX RT, check out the

i.MX RT fact sheet

or visit

i.MX RT Crossover MCUs