# BSC913x IPC Architecture

FTF-ENT-F0130

#### **Wim Rouwet**

Senior Systems Architect

#### June 2012

Freescale, the Freescale logo. AltiVec, C-5, CodeTEST, CodeWarrior, ColdFire, ColdFire, C-Ware, the Energy Efficient Solutions logo, Kinetis, mobileGT, PowerQUICC, Processor Expert, OorlQ, Oorivva, StarCore, Symphony and VortiQa are trademarks of Freescale Semiconductor, Inc., Reg. U.S. Pat. & Tm. Off. Airfast, BeeKit, BeeStack, CoreNet, Flexis, Magniyi, MXC, Platform in a Package, Cord Qonverge, OuICC Engine, Ready Play, SafeAssure, the SafeAssure logo, SMARTMOS, TurboLink, Vybrid and Xtrinsic are trademarks of Freescale Semiconductor, Inc. All other product or service names are the property of their respective owners. © 2012 Freescale Semiconductor.

# **Agenda**

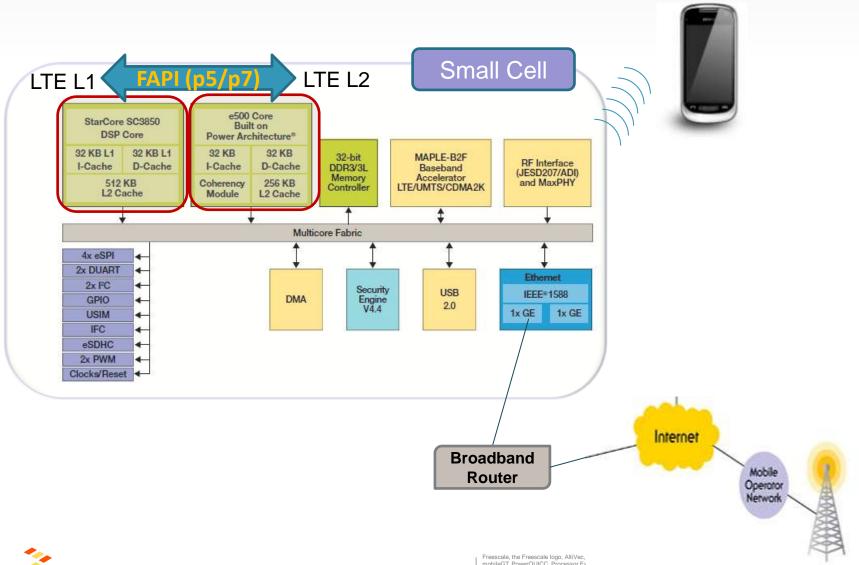

- Small-Cell Internals

- Small Cell based on BSC9131

- BSC913x Software Architecture

- IPC Architecture

- FAPI Messages to IPC Channel binding

- Use Cases

- Q&A

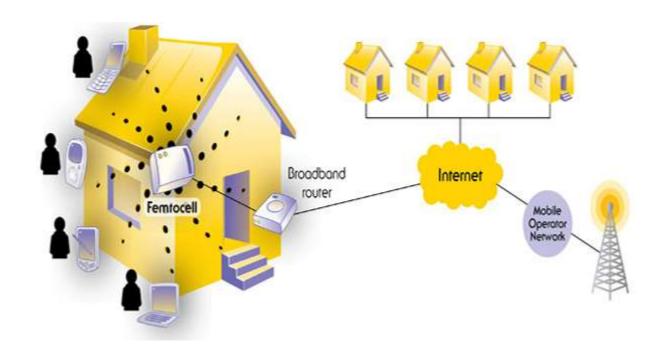

#### **Small Cell**

- Small Cell = Home or small office cellular base stations supporting the following standards:

- LTE-FDD/TDD

- WCDMA (HSPA+)

- CDMA2K

- TD-SCDMA

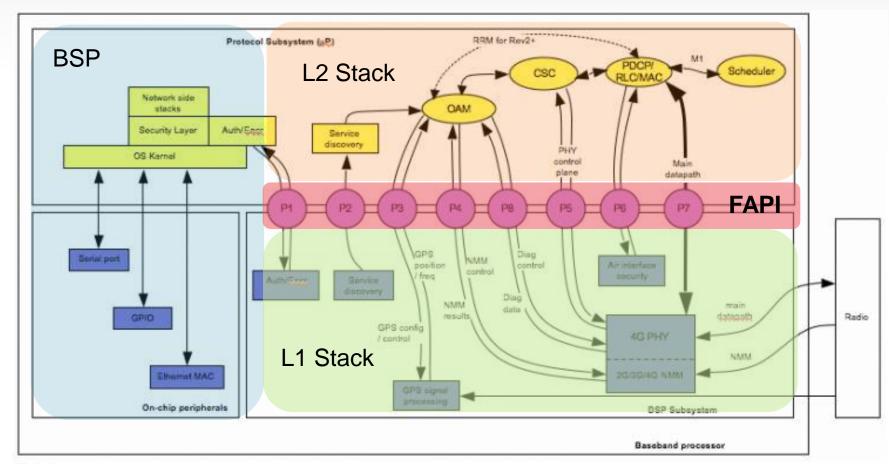

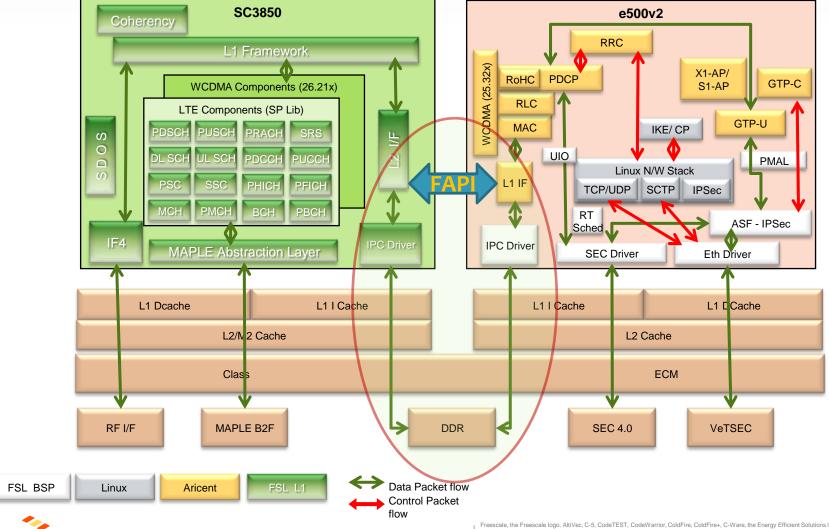

# Software Components in a Small Cell

#### **FAPI:**

Small Cell Forum Femto Application Programming Interface

#### Internals of a Freescale-Powered Small Cell

# Femto/Pico-Cell (913x) System Architecture

## **IPC Design Highlights**

- Shared Library

- Provides Zero Copy

- Lock Free, No synchronization required

- Independent Unidirectional Channels

- Single Producer Single Consumer

- Multicore Ready

### Achieving zero-copy operation

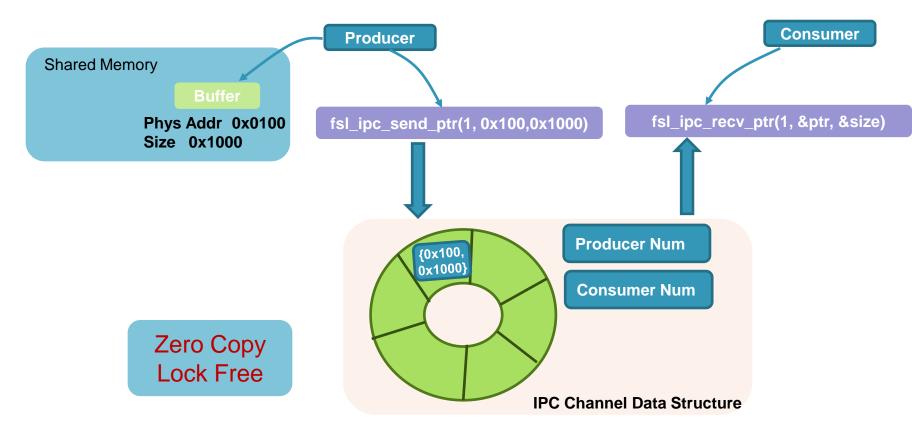

#### **IPC Channels**

- Pointer Channel

- Producer allocates memory and provides consumer the pointer via this channel.

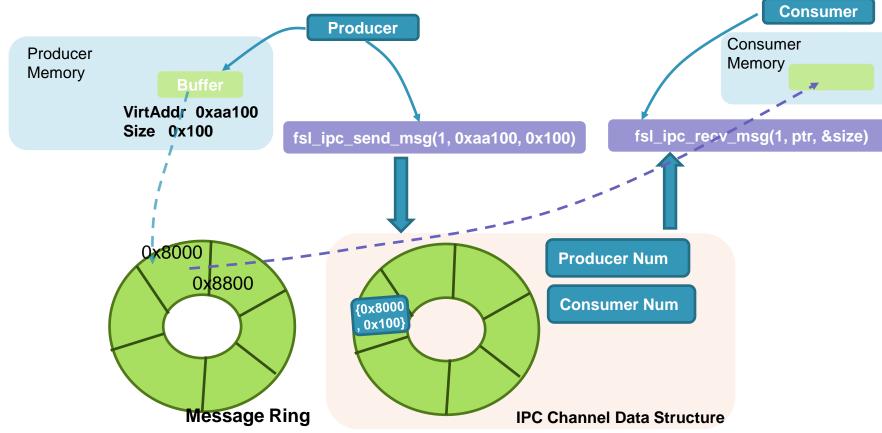

#### **IPC Channels**

- MSG Channel

- For small messages. IPC copies producer buffer in a message ring. IPC later copies the message from message ring to consumer buffer.

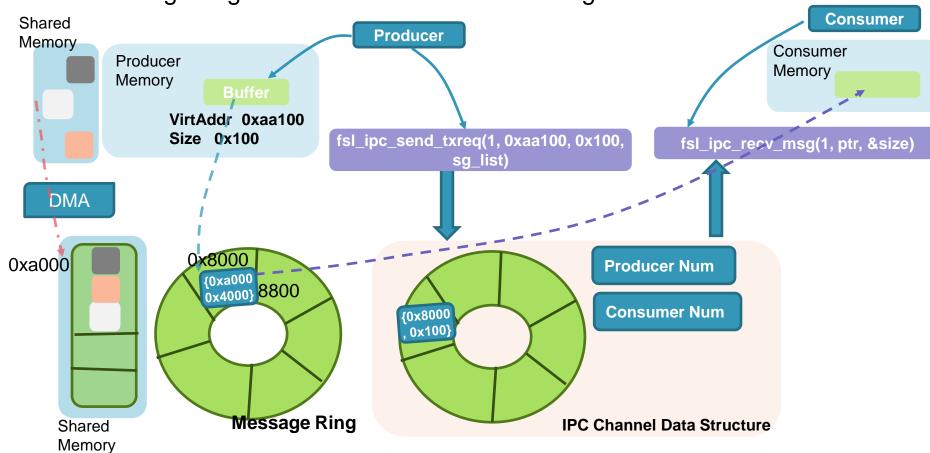

#### **IPC Channels**

*freescale*™

- Tx Request Channel

- For small messages and large PDU's. IPC copies producer buffer in a message ring and uses DMA to linearize fragmented PDUs.

# **FAPI Messages to IPC Channels Binding**

L2=> L1 requests **PARAM CONFIG** L1=>L2 response/indications **START PARAM Response STOP** Message **CONFIG Response** Channel **UL\_CONFIG STOP Indicator DL CONFIG ERROR Indicator** HI\_DIC0 **Subframe Indicator TxRequest** L2=>L1 Channel **RX\_ULSCH** Tx.Request **HARQ CRC** RX SR RX CQL **Pointer** Channel **RACH** SRS

#### **Performance and Optimizations**

- Consumer Message Channels towards DSP can be placed in M2 memory for faster access

- Zero Copy is achieved in Tx.Request where the average buffer size is 9k, as DMA is involved

- IPC uses static binding of channels at compile time, channel numbers are integer values.

- L1/L2 share a common header file with channel numbers as constants

# **Scalability**

- On a multicore system Channels can be distributed among cores to do load balancing.

- Same L2 stack can run on 9131,9132 and future architectures with minimal changes.

#### Conclusions

- SW optimization is key to achieve performance

- Zero-copy through use of DMA engine

- Driver optimization to application

- Tight integration with L1 and L2 stacks drives optimized solution

### References

• [1] Small Cell Forum Specifications