# IBIS Overview and Model Usage

**Kevin Lam**

APF-NET-T0882

Freescale, the Freescale logo, AltiVec, C-S, CodeTEST, CodeWarrior, ColdFire, ColdFire+, C-Ware, the Energy Efficient Solutions logo, Kinetis, mobileGT, PEG, PowerOUICC, Processor Expert, QorlQ, Qoriwa, SafeAssure, the SafeAssure logo, StarCore, Symphony and VortiQa are trademarks of Freescale Semiconductor, Inc., Reg. U. S. Pat, & Tm. Qff. Airfast, BeeKit, BeeStack, CoreNet, Flexis, Leyerscape, Magniyi, MXC, Pletform in a Package, OorfQ Converge, QUICC Engine, Ready Play, SMARTMOS, Tower, TurboLink, Vybrid and Xtrinsic are trademarks of Freescale Semiconductor, Inc. All other product or service names are the property of their respective owners. @ 2013 Freescale Semiconductor, Inc.

### **Agenda**

- IBIS Overview

- What is IBIS

- How is IBIS Used?

- IO buffer timing and noise issues

- Need for IO buffer models

- IO Buffer Modeling Options

- SPICE vs IBIS

- IBIS Details

- Details of Electrical Models and Full Device IBIS

- Examples

- Clock, edge rate, DDR

# **IBIS Overview**

Freescale, the Freescale logo, AltiVec, C-5, CodeTEST, CodeWarrior, ColdFire, ColdFire+, C-Ware, the Energy Efficient Solutions logo, Kinetis, mobileGT, PEG, PowerQUICC, Procesous Expert, CorlO, Qoriva, SafeAssure, the SafeAssure logo, StarCore, Symphony and VortiQa are trademarks of Freescale Semiconductor, Inc., Reg. U.S. Pat. & Tm. Off. Airlast, BeeKit, BeeStack, OcreNet, Flexis, Layerscape, MagniV, MXC, Platform in a Package, QorlQ Qonverge, QUICC Engine, Ready Play, SMARTMOS, Tower, TurboLink, Vybrid and Xtrinsic are trademarks of Freescale Semiconductor, Inc. All other product or service names are the property of their respective owners. © 2013 Freescale Semiconductor, Inc.

#### What is IBIS?

- IBIS is one piece of design collateral that FSL NMSG/NPD delivers

- Fills the need to simulate the IO buffers from the devices on a bus

- Not a power model, not a bus functional model

- IBIS: Input/Output Buffer Information Specification

- What is IBIS?

- Not a model, like a SPICE model

- Tabular description of the IO buffer characteristics

- Simulators interpret data in IBIS to produce a model

#### What is IBIS?

- Background when/where did it start?

- Behavioral Modeling

- Based on properties of IO

- IBIS Specification 1.0: April 1993

- Intel credited with driving standard development for use with PCI Bus analysis and simulation

- Same Era as PCI Spec:

- Edge Rates Faster

- Lumped Loads not as prevalent; move to distributed loads and transmission lines

- Subsequent key versions:

- 2.1: December 1995

- **3.2:** September 1999

- 5.0: August 2008

- 5.1: August 2012

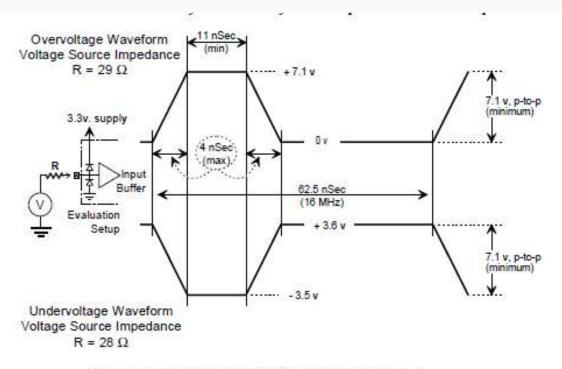

# IV data spec from PCI Spec

Figure 4-5: V/I Curves for 3,3V Signaling

## Receiver Data from PCI Spec

Figure 4-6: Maximum AC Waveforms for 3.3V Signaling

#### What is IBIS – Where is it used?

- What consumes/uses IBIS? What does IBIS feed?

- Used by multiple EDA tools for signal integrity and timing simulations

- EDA tools have models for the interconnect between devices

- IO buffer models are needed to drive and receive signals that use the interconnect in the design (typically PCB)

- EDA tools customers use:

- Cadence PCB SI (translates to Cadence DML model)

- Mentor Hyperlynx

- Synopsys HSPICE

- Agilent ADS

- Sigrity Speed 2000

- Altium

# How is IBIS Used?

Freescale, the Freescale logo, AltiVec, C-5, CodeTEST, CodeWarrior, ColdFire, ColdFire+, C-Ware, the Energy Efficient Solutions logo, Kinetis, mobileGT, PEG, PowerQUIJCC, Processor Expert, QorlQ, Qoriva, SafeAssure, the SafeAssure logo, StarCore, Symphony and VortiQa are trademarks of Freescale Semiconductor, Inc., Reg. U.S. Pat. 8. Tm. Off. Airfast, Beekit, BeeStack, CoreNet, Flexis, Layerscape, Magniyi MXC, Platform in a Package, QorlQ Converge, QUIJCC Engine, Ready Play, SMARTMOS, Tower, TurboLink, Vybrid and Xtrinsic are trademarks of Freescale Semiconductor, Inc. All other product or service names are the property of their respective owners. © 2013 Freescale Semiconductor, Inc.

## **Example Timing Budget**

- Timing Budgets Include Driver, Receiver, Interconnect

- IBIS is used for predicting how the driver interacts with the interconnect

- IBIS is used for predicting how the receiver interacts with the interconnect

| Element      | Skew Component                     | DDR3-800 |      | DDR3-1066 |      |      |                                                                                            |

|--------------|------------------------------------|----------|------|-----------|------|------|--------------------------------------------------------------------------------------------|

|              |                                    | Setup    | Hold | Setup     | Hold | Unit | Comments                                                                                   |

| Clock        | Data/strobe chip PLL jitter        | 45       | 45   | 45        | 45   | ps   |                                                                                            |

|              | DRAM <sup>1</sup> JITper           | 50       | 50   | 45        | 45   | ps   | Derate what the DRAM is tested for                                                         |

|              | Clock skew                         | 0        | 0    | 0         | 0    | ps   |                                                                                            |

| Transmitter  | Controller skew                    | 267      | 267  | 209       | 209  | ps   | Assume similar to DRAM and use<br>DRAM's specifications                                    |

| Interconnect | DQ crosstalk and ISI               | 52       | 52   | 32        | 32   | ps.  | 1 victim (1010), 4 aggressors (PRBS)                                                       |

|              | DQS crosstalk and ISI <sup>1</sup> | 23       | 23   | 23        | 23   | ps   | 1 shielded victim (1010). 2 aggresson<br>(PRBS)                                            |

|              | Vref reduction                     | 10       | 10   | 10        | 10   | ps   | ±30mV in DRAM skew, additional<br>±10 mV/(1 V/ns)                                          |

|              | Reff mismatch                      | 0        | 0    | 0         | 0    | ps   | ±6% accounted for by DRAM specification                                                    |

|              | Path matching (board)              | 10       | 10   | 10        | 10   | ps   | Within byte lane: 165 ps/in; mismatch within DQS to DQ                                     |

|              | Path matching (module)             | 5        | 5    | 5         | 5    | ps   | Module routing skew (30% reduction<br>with leveling)                                       |

|              | Input capacitance<br>matching      | 5        | 5    | 5         | 5    | ps   | Strobe to data variation                                                                   |

|              | ODT skew (1%)                      | 5        | - 5  | 5         | 5    | ps   | Estimated                                                                                  |

|              | Total interconnect                 | 110      | 110  | 90        | 90   | ps   |                                                                                            |

| Receiver     | DRAM skew                          | 215      | 215  | 165       | 165  | ps   | <sup>1</sup> DS, <sup>1</sup> DH from DRAM specification,<br>derated for faster slew rates |

| Total loss   | Total skew                         | 592      | 592  | 464       | 464  | ps   | Transmitter + receiver + interconnect skews                                                |

| MAX eye      | Time available                     | 625      | 625  | 469       | 469  | ps   | Total time available                                                                       |

| Budget (4L)  | Timing margin                      | 33       | 33   | 5         | 5    | ps   | 4-layer (microstrip) 40Ω, 0.135mm trace<br>to trace                                        |

### **Predicting Effect of the Interconnect**

How to calculate the system effects when interfacing with our devices? How is the digital design implemented in the physical world (typically printed circuit board)?

#### Drivers interact with interconnect

- Driver impedance

- Driver edge rate

- De-emphasis/Equalization

#### Receivers interact with interconnect and effect driver

- Capacitive load

- Receiver clamping

- Termination

- Equalization

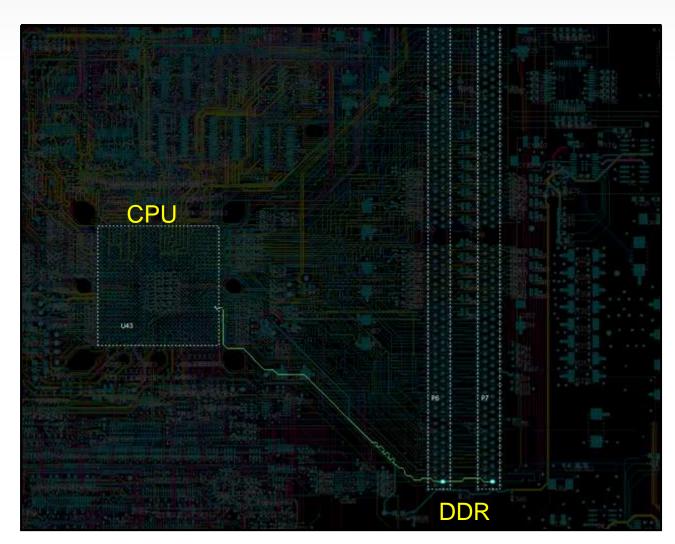

## **Board Layout Example: DDR Memory**

How to predict behavior of the CPU driving the DDR DIMMs?

**Driver: CPU**

Drive strength

#### Interconnect:

- Package

- PCB Traces

- DIMM Sockets

- DIMM routing

- Crosstalk

Receiver: Memory

ODT

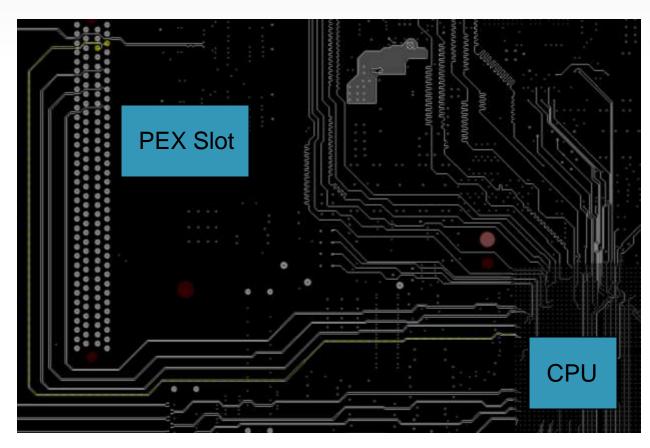

## **Board Layout Example: SERDES**

Will the PCB

Interconnect degrade data eye from CPU to connector?

**Driver: CPU**

Equalization

#### Interconnect:

- Package

- PCB Traces/Vias

- Connector

- Crosstalk

#### Receiver:

- Termination

- Equalization

# **Board Layout Example: Slower Speed Bus**

Slow Clock

What if Routing to Clock Load is not at end of net?

How do edge rates affect solution?

What simulation options are available?

# IO Buffer Modeling Background

Freescale, the Freescale logo, AltiVec, C-S, CodeTEST, CodeWarrior, ColdFire, ColdFire, ColdFire, Efficient Solutions logo, Kinetis, mobileGT, PEG, PowerQUICC, Processor Expert, OdriQ, Qorivva, SafeAssure, the SafeAssure logo, StarCore, Symphony and VortiQa are trademarks of Freescale Semiconductor, Inc., Reg. U.S., Pat. & Tm. Off. Airfast, Beekit, Beekitack, OcreNet, Flexis, Layerscape, MagniV, MXC, Platform in a Package, QorlQ Converge, QUICC Engine, Ready Play, SMARTMOS, Tower, TurboLink, Vybrid and Xtrinsic are trademarks of Freescale Semiconductor, Inc. All other product or service names are the property of their respective owners. @ 2013 Freescale Semiconductor, Inc.

## **IO** Buffer Modeling

How to model the IO buffers?

#### **Driver Model:**

- Linear value:  $Z_D = R_D$

- IV data use in Bergeron Plots

- Circuit Model

#### **Receiver Models:**

- Lumped capacitor

- IV data

- Circuit Model

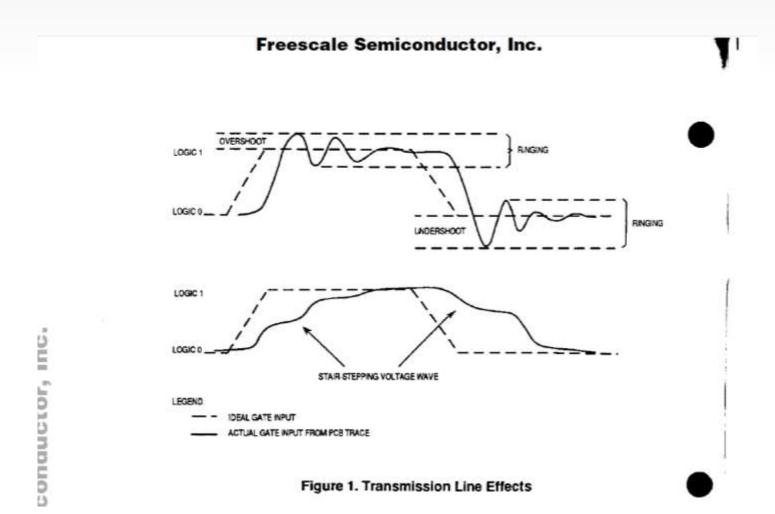

#### **Transmission Line Effects**

semiconductor,

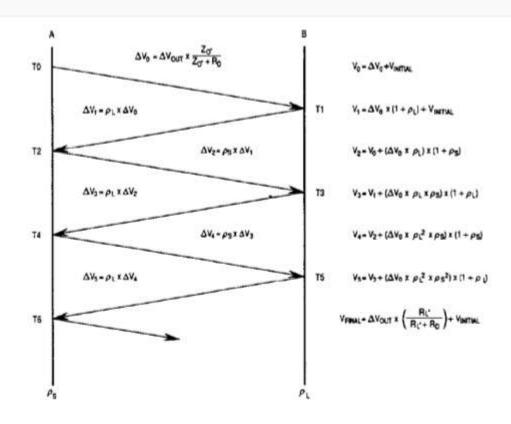

## **Lattice Diagram**

NOTE: \( \rho\_t \) and \( \rho\_s \) are reflection coefficients and \( V\_{\text{INTIME}} \) is the steady-state voltage prior to the switching of the gate. Each TD is a propagation delay(\( T\_{\text{PQ}} \)) in duration. A and B indicate the driving and receiving ends of the trace, respectively.

(a) Lattice Diagram

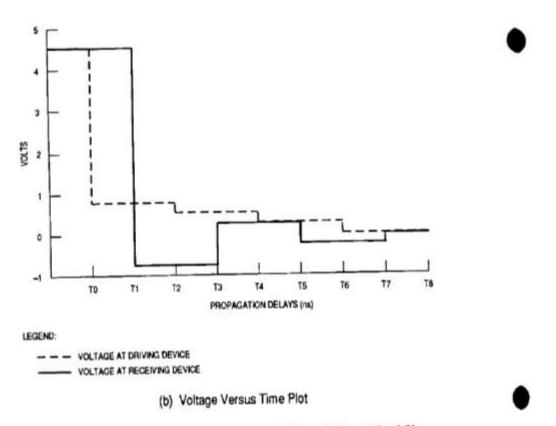

# **Voltage Plot from Lattice Diagram**

Figure 5. Lattice Diagram Representations (Sheet 2 of 2)

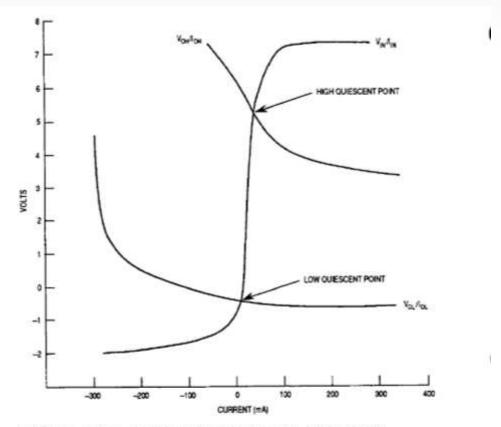

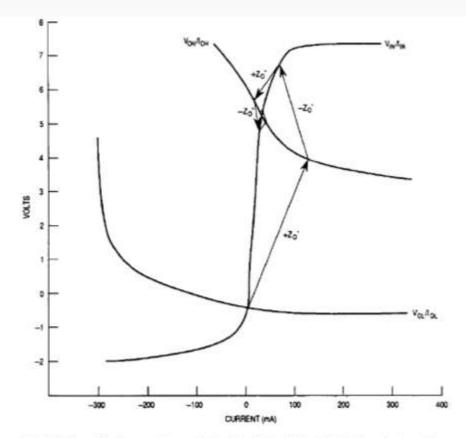

## Bergeron Plot – overlay device IV curves

NOTE: V<sub>DL</sub>/I<sub>DL</sub> and V<sub>DL</sub>/I<sub>DL</sub> are output curves for the driving device; V<sub>DL</sub>/I<sub>DL</sub> is the input outve for the receiving device.

Figure 6. Bergeron Plot

# **Bergeron Plot with Interconnect Impedance**

NOTE: V<sub>OL</sub>/I<sub>OL</sub> and V<sub>OL</sub>/I<sub>OH</sub> are output curves for the driving device; V<sub>M</sub>/I<sub>M</sub> is the input curve for the receiving device; and Z<sub>d</sub> is the loaded characteristic impedance of the trace.

Figure 7. Bergeron Plot with Transitions

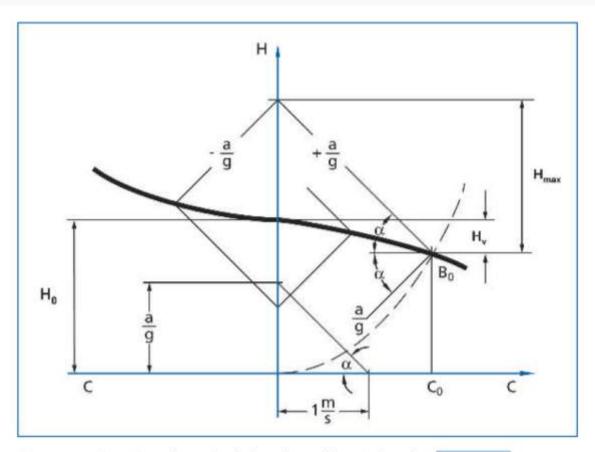

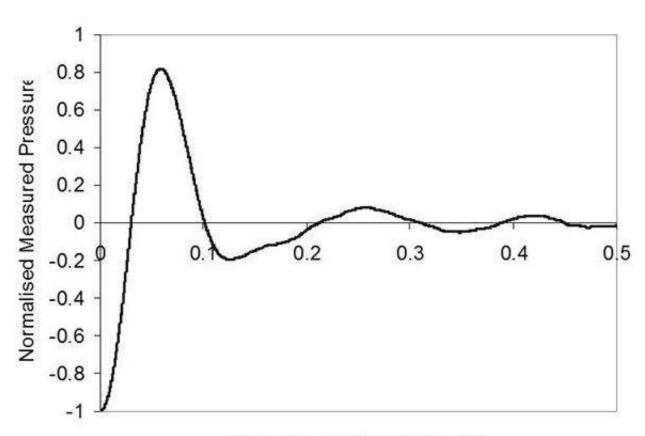

# **Bergeron Graphical Method for Water Hammer**

Fig. 7-1: Graphical method developed by Schnyder-Bergeron

#### **Water Hammer Pressure**

Time Since Valve Closing (s)

# \_stailed IO Buffer Modeling Solution: SPICE and IBIS

- Better means that linear models:

- SPICE

- Behavioral

- SPICE solutions used for circuit design

- Based on IO buffer's physical dimensions

- SPICE has long runtime for layout-based (most accurate) IOs

- SPICE could have proprietary buffer design and process information

- SPICE models may not easily work together if global parameters are used in IO models.

- IBIS fast runtime and data descriptive of IO buffer

# Details of IBIS: What are the pieces?

Freescale, the Freescale logo, AltiVec, C-5, CodeTEST, CodeWarrior, ColdFire, ColdFire+, C-Ware, the Energy Efficient Solutions logo, Kinetis, mobileGT, PEG, PowerQUIJCC, Processor Expert, Corfl.Q, coriva, SafeAssure, the SafeAssure logo, StarCore, Symphony and VortiCa are trademarks of Freescale Semiconductor, Inc., Reg. U.S. Pat. & Tm. Off. Airfast, Beekit, Beekit, Beekitack, CoreNet, Flexis, Layerscape, Magnit/, MXC, Platform in a Package, Corfl Converge, QUIJCC Engine, Ready Play, SMARTMOS, Tower, TurboLink, Vybrid and Xtrinsic are trademarks of Freescale Semiconductor, Inc. All other product or service names are the property of their respective owners. © 2013 Freescale Semiconductor, Inc.

#### **Elements of IBIS**

Data needed for electrical modeling of the IO:

- Electrical Data

- Hardware Specification Data

- Pin Listing

- Package Data

# Details of IBIS: How to derive the electrical model data?

Freescale, the Freescale logo, AltiVec, C-5, CodeTEST, CodeWarrior, ColdFire, ColdFire+, C-Ware, the Energy Efficient Solutions logo, Kinetis, mobileGT, PEG, PowerQUICC, Procesor Expert, Corfl.Q, Coriva, SafeAssure, the SafeAssure logo, SlarGore, Symphony and VortiGa are trademarks of Freescale Semiconductor, Inc., Reg. U.S. Pat. & Tm. Off. Airlast, Beelkit, BeelStack, CoreNet, Flexis, Layerscape, MagniV, MXC, Platform in a Package, QorlQ Qonverge, QUICC Engine, Ready Play, SIMARTMOS, Tower, TurbcLink, Vybrid and Xtrinsic are trademarks of Freescale Semiconductor, Inc. All other product or service names are the property of their respective owners. © 2013 Freescale Semiconductor, Inc.

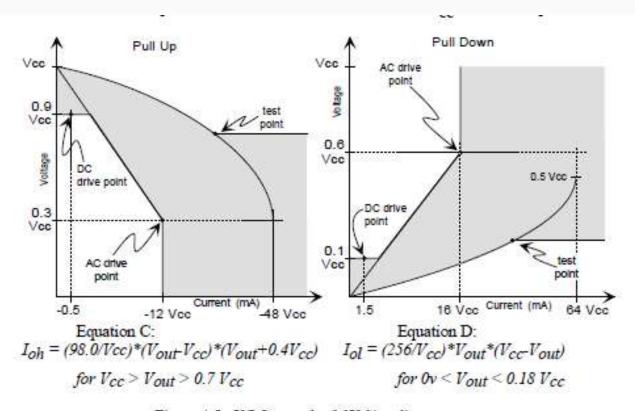

#### **Elements of IBIS: Electrical Data**

#### DC IV Data

- Pulldown

- Pullup

- Ground Clamp

- Power Clamp

#### Transient (Voltage vs. Time) Data

- Ramp or dv/dt ratio

- VT: rising, pulled low

- VT: rising, pulled high

- VT: falling, pulled low

- VT: falling, pulled high

#### Data is simulated or measured across process, voltage, temperature

- IBIS min: worst-case drive (slow process, low voltage, high temperature)

- IBIS typ: typical-case drive (typ process, typ voltage, typ temperature)

- IBIS max: best-case drive (fast process, high voltage, low temperature)

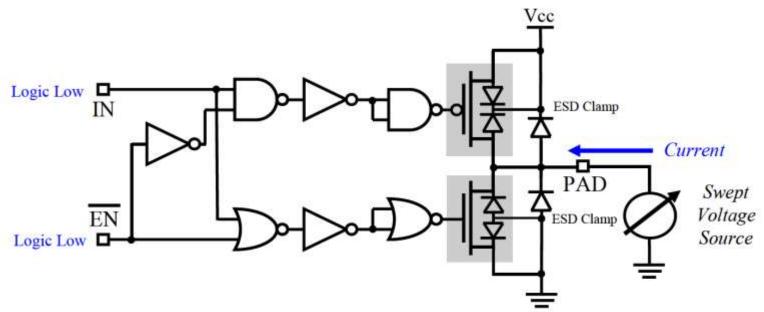

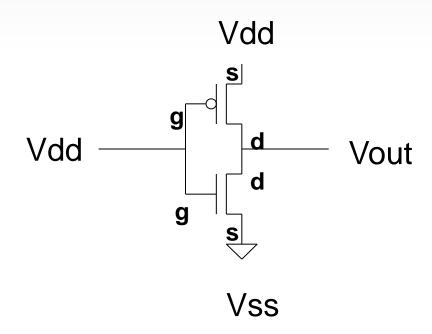

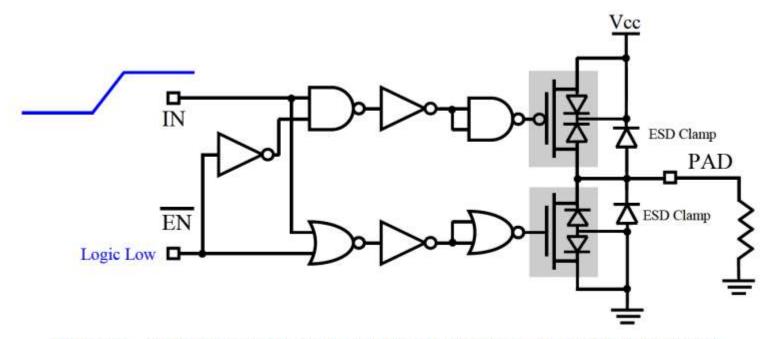

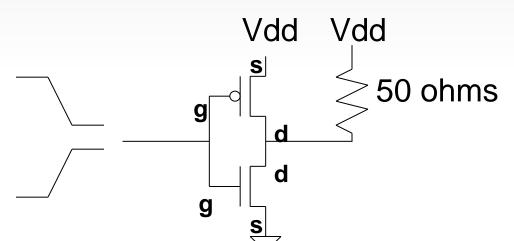

### From IBIS Cookbook

Figure 3.1 - Standard 3-state Buffer (Pulldown I-V Table Extraction Shown)

#### DC IV Data: Pulldown

#### Pulldown Extraction:

Excite Pulldown (e.g. NMOS)

Sweep I vs. -Vdd to 2Vdd

File: 7448\_25v\_r4\_Model: busio\_25\_rev1\_1 (Fulldown, Ground relative)

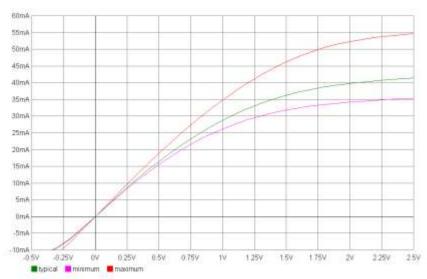

## DC IV Data: Pullup

Pullup Extraction:

Excite Pullup (e.g. PMOS)

Sweep I vs. -Vdd to 2Vdd

File: 7448\_25v\_r4, Modet busio\_25\_rev1\_1 (Pullup, Vcc relative)

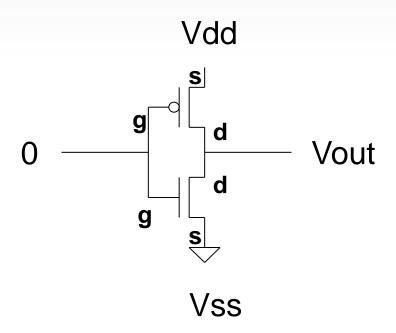

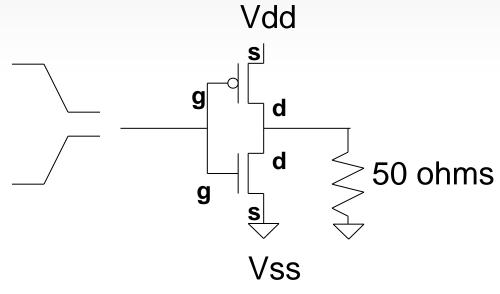

### From IBIS Cookbook

Figure 3.2 - Simulation Setup for Extracting Ramp Rate Information (Rising Edge Shown)

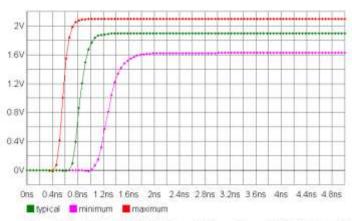

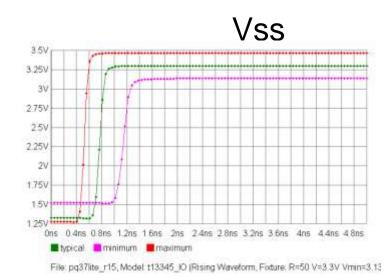

### **Transient Data: 50 ohm resistor tied to Ground**

Rising and Falling Voltage vs. Time table with 50 ohm resistive load tied low

File: pg37lite\_r15, Model t13345\_IO (Rising Waveform, Fixture: R=50 V=0V Vmin=0V Vm

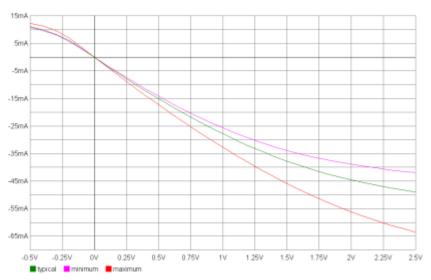

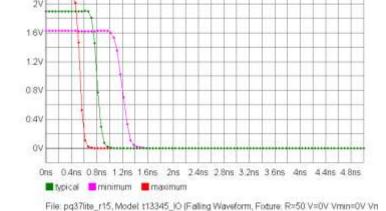

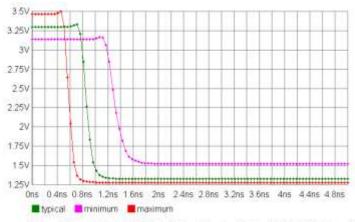

### **Transient Data: 50 ohm resistor tied to VDD**

Rising and Falling Voltage vs. Time table with 50 ohm resistive load tied high

File: pg37lite: r15, Model: t13345\_IO (Falling Waveform, Fixture: R=50 V=3.3V Vmin=3.1)

### **Elements of IBIS: Hardware Spec Related Data**

#### Signal name and buffer description items:

- Pin List

- Signal to IO buffer model map

- Programmable/selectable drive strength IOs

- Differential pair map

#### Operating conditions and Hardware Spec value items:

- OVdd: min, typ, max

- Temperature: min, typ, max

- Test Load: Vmeas, Vref, Cref, Rref

- Input voltage levels: Vinl, Vinh

- Overshoot and undershoot levels

# **IBIS** Correlation

Freescale, the Freescale logo, AltiVec, C-5, CodeTEST, CodeWarrior, ColdFire, ColdFire+, C-Ware, the Energy Efficient Solutions logo, Kinetis, mobileGT, PEG, PowerQUICC, Processor Expert, Conf.Q. Ooriva, SafeAssure, the SafeAssure logo, StarCore, Symphony and VortiQa are trademarks of Freescale Semiconductor, Inc., Reg. U.S. Pat. & Tm. Off. Airfast, Beekit, Beekit, BeeStack, CoreNet, Flexis, Layerscape, MagniV, MXC, Platform in a Package, QarlQ Qonverge, QUICC Engine, Ready Play, SMARTMOS, Tower, TurboLink, Vybrid and Xtrinsic are trademarks of Freescale Semiconductor, Inc. All other product or service names are the property of their respective owners. © 2013 Freescale Semiconductor, Inc.

#### **IBIS Development and Checking Procedure**

- IBIS Checker Status

- IBIS checked using 3.2, 4.1, 5.0 checkers

- Visual IBIS inspection

- Warnings reviewed

- Simulation Comparison

- IBIS-based simulations vs. internal SPICE

- Measured IBIS

- Tester-based IBIS data

- Allows IBIS to track actual silicon and process updates

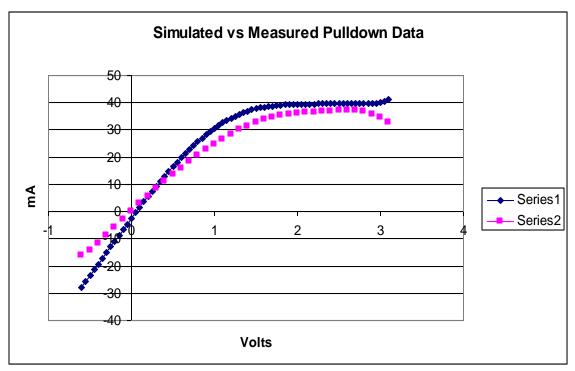

#### Measured vs. Simulated Pulldown Data

Blue is measured; purple is simulated

### **Example IBIS-based Simulations**

Freescale, the Freescale logo, AltiVec, C-5, CodeTEST, CodeWarrior, ColdFire, ColdFire+, C-Ware, the Energy Efficient Solutions logo, Kinetis, mobileGT, PEG, PowerQUICC, Processor Expert, CorfQ, Coriva, SafeAssure, the SafeAssure logo, StarCore, Symphony and VortiCa are trademarks of Freescale Semiconductor, Inc., Reg. U.S. Pat. 8. Tm. Off. Airlast, Beeklt, BeekStack, CoreNet, Flexis, Layerscape, MagniV, MXC, Platform in a Package, CorfQ converge, QUICC Engine, Ready Play, SMARTMOS, Tower, TurboLink, Vybrid and Xtrinsic are trademarks of Freescale Semiconductor, Inc. All other product or service names are the property of their respective owners. © 2013 Freescale Semiconductor, Inc.

#### **IBIS-based simulation examples**

- Examples of problems IBIS can help evaluate:

- 1) Slow Bus Daisy Chain Route

- Vary Edge Rate and Terminations

- 2) Input Signal Edge Rate

- Clock Signal Edge Rate → need to meet FSL clock input timing specs

- 3) Input (Read) Signal Quality

- Look at Die vs Pin

- 4) DDR Read Signal

- 5) DDR write timing

- DDR3-1866 with two DIMM slots

- Simulate to measure which DIMM slot has best signal quality and timing

# 1) Daisy Chain Load Vary Edge Rate, Termination

Freescale, the Freescale logo, AltiVec, C-5, CodeTEST, CodelWarrior, ColdFire, ColdFire+, C-Ware, the Energy Efficient Solutions logo, Kinetis, mobileGT, PEG, PowerQUICC, Processor Expert, Corf.Q, Corivva, SafeAssure, the SafeAssure logo, StarCore, Symphony and VortiCua are trademarks of Freescale Semiconductor, Inc., Reg. U.S. Pat. & Tm. Off. Airlast, Beeklit, BeesStack, CoreNet, Flexis, Layerscape, Magnivi, MXC, Platform in a Package, CorfQ converge, QUICC Engine, Ready Play, SMARTMOS, Tower, TurbcLink, Vybrid and Xtrinsic are trademarks of Freescale Semiconductor, Inc. All other product or service names are the property of their respective owners, © 2013 Freescale Semiconductor, Inc.

#### **Board Layout Example: Slower Speed Bus**

Slow Clock

What if Routing to Clock Load is not at end of net?

How do edge rates affect solution?

What simulation options are available?

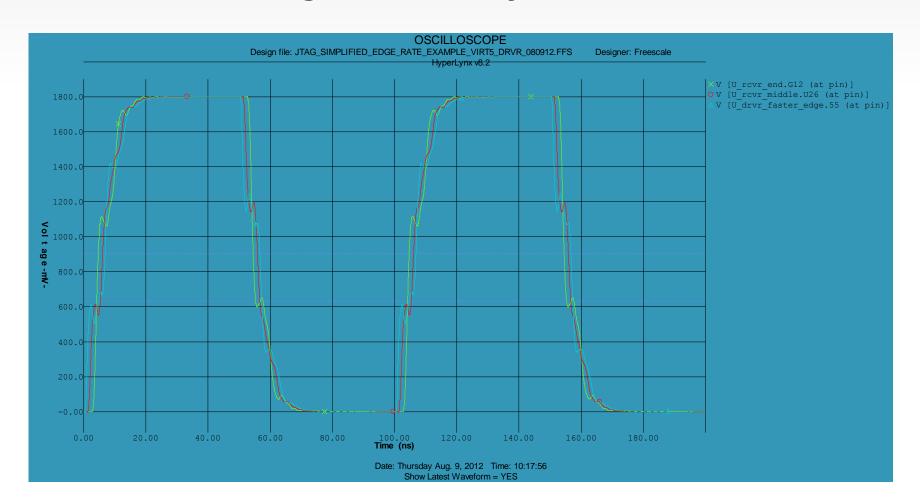

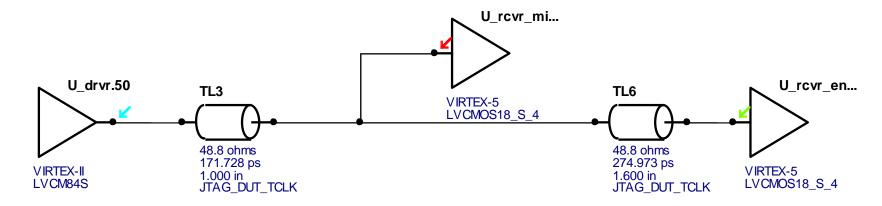

#### **Slow Edge Rate Daisy Chain**

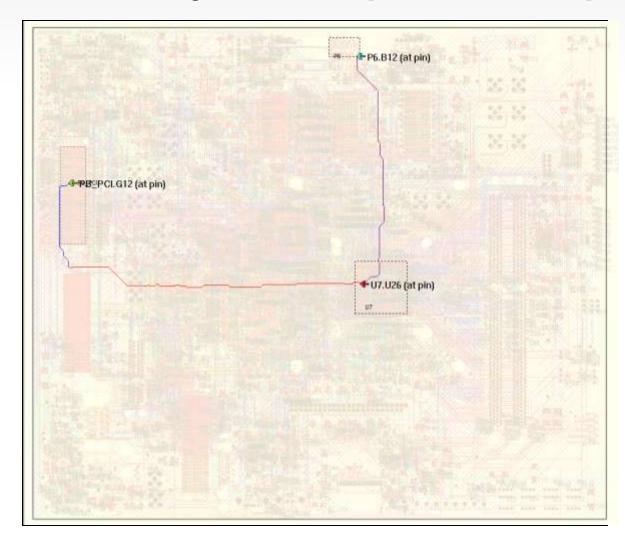

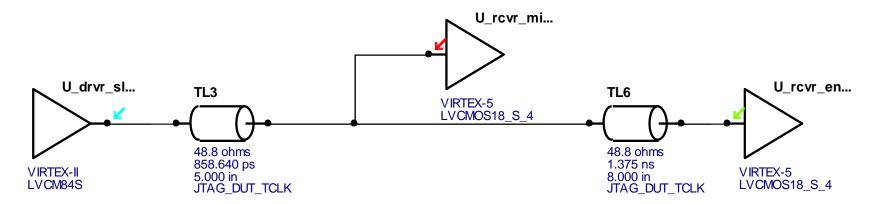

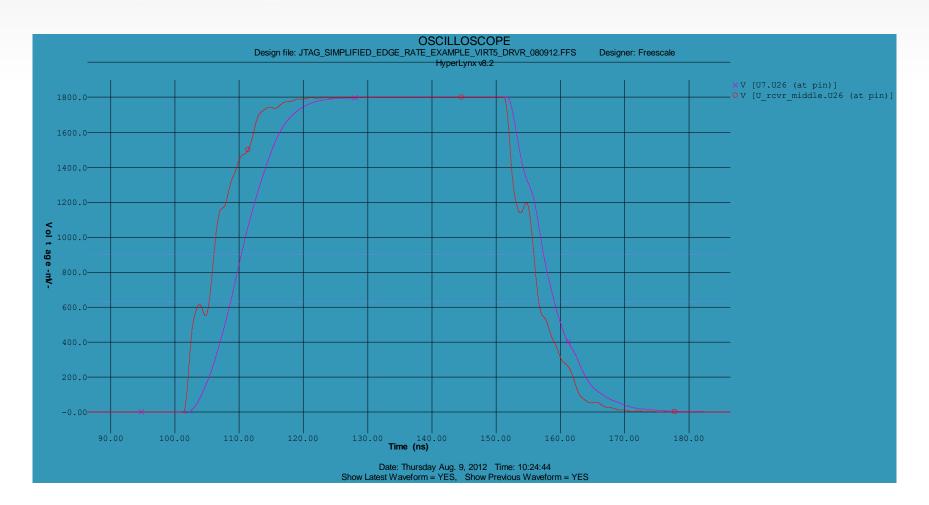

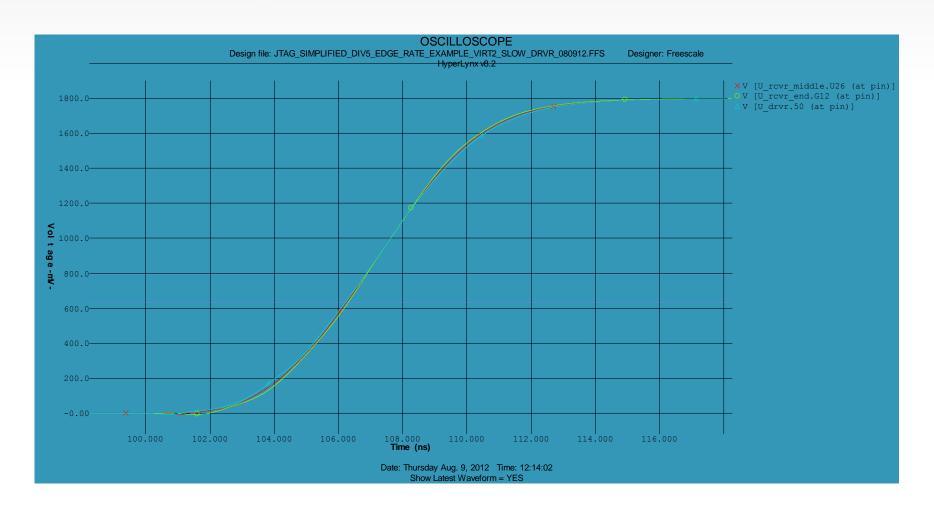

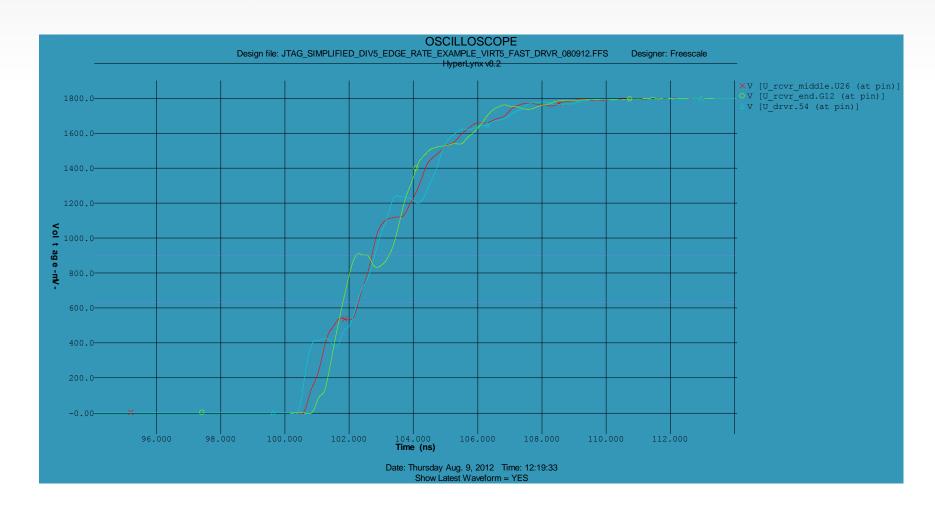

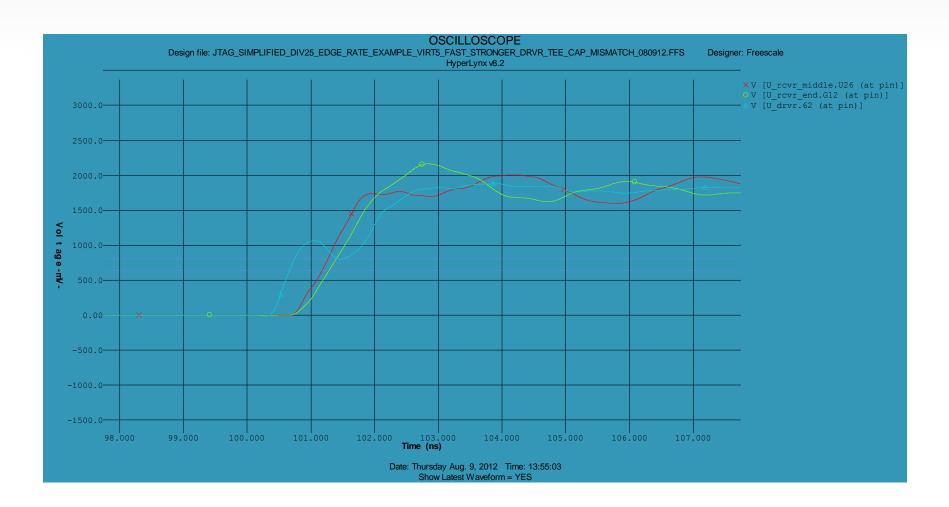

Design File: JTAG\_simplified\_edge\_rate\_example\_virt2\_dvr\_080912ffs HyperLynxLineSmv8.2

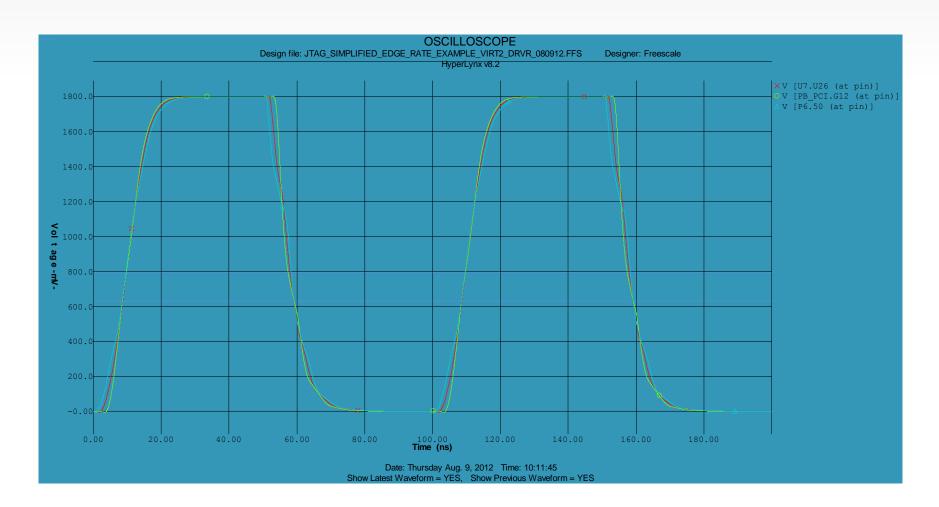

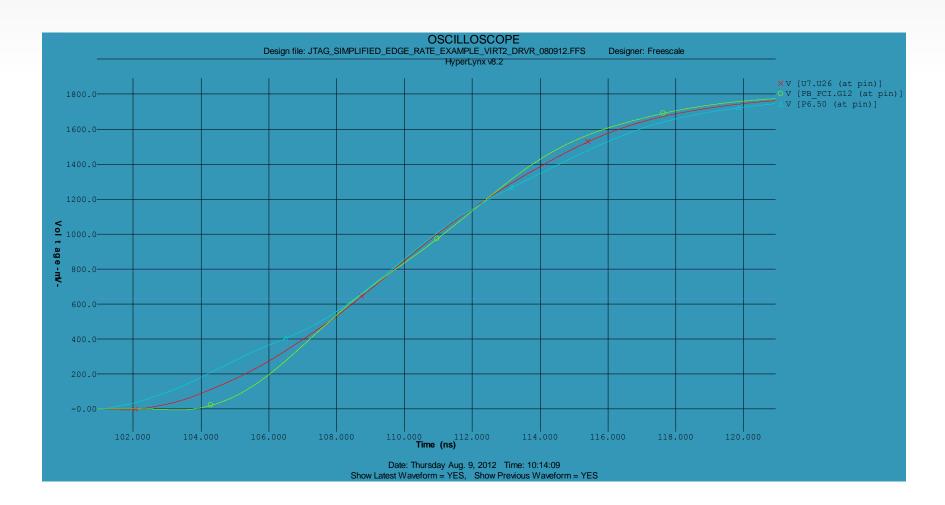

#### **Slow Edge Rate Daisy Chain**

#### **Slow Edge Rate Daisy Chain**

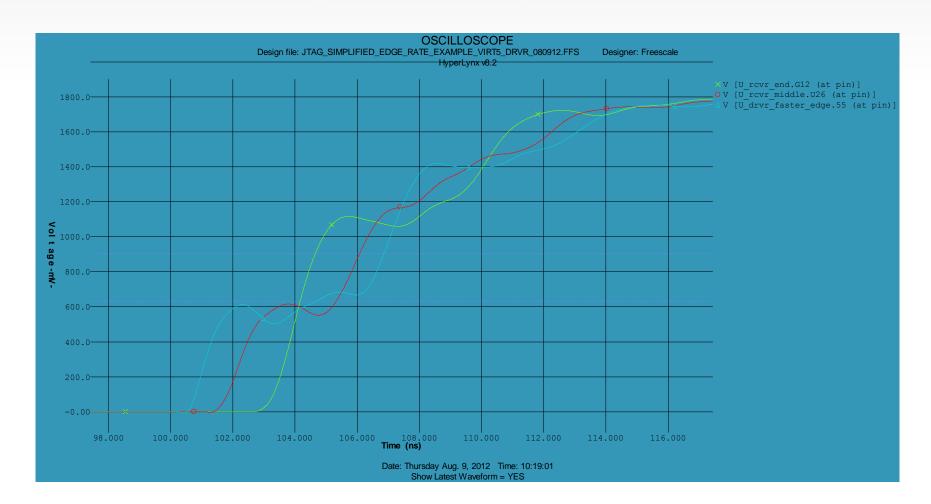

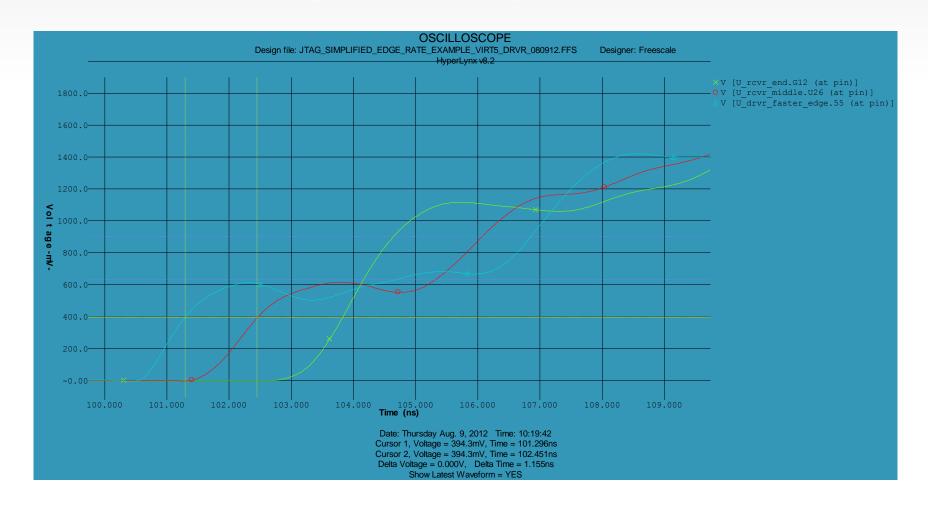

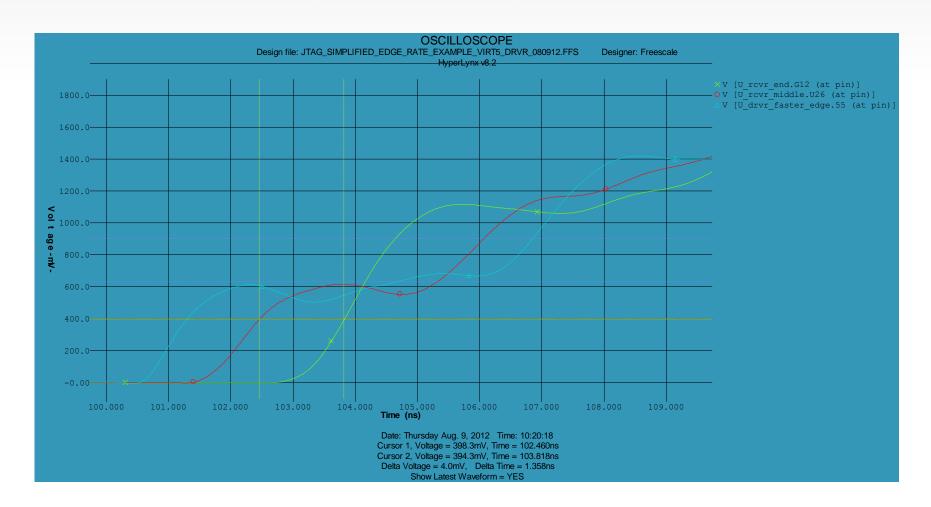

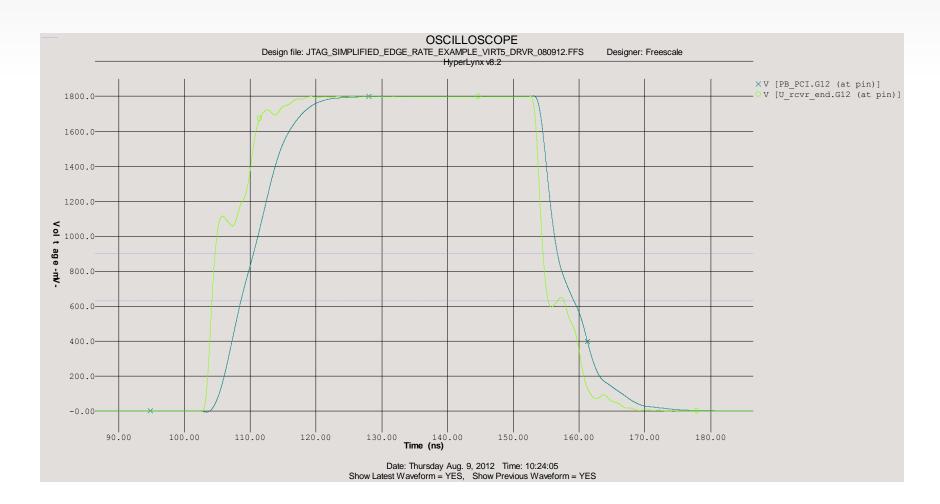

#### **Compare Edge Rate Waveforms**

#### **Compare Edge Rate Waveforms**

#### **Shorten lengths: Slow Driver**

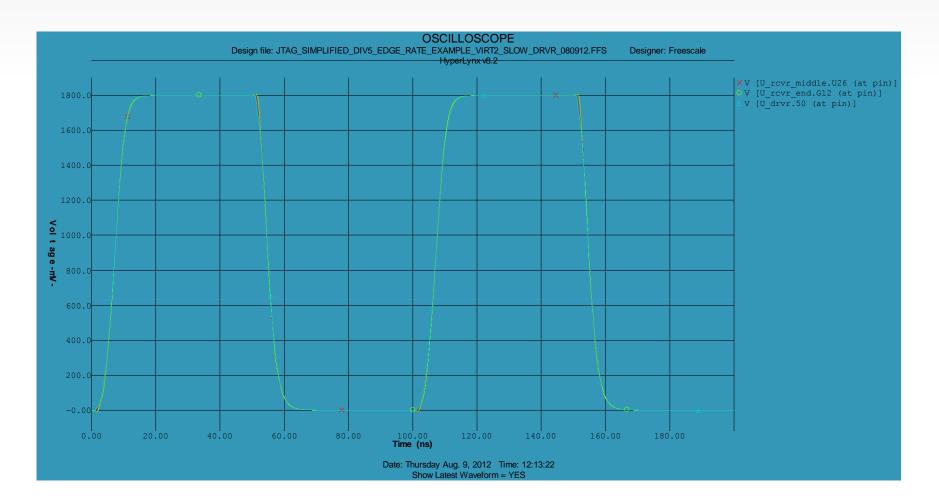

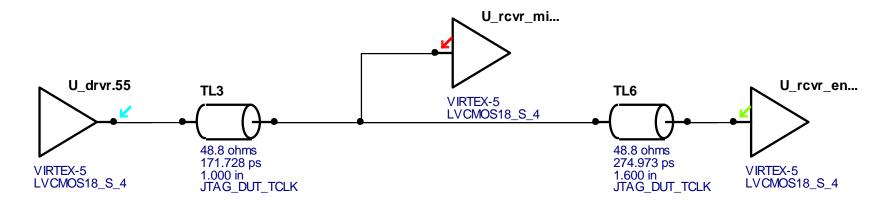

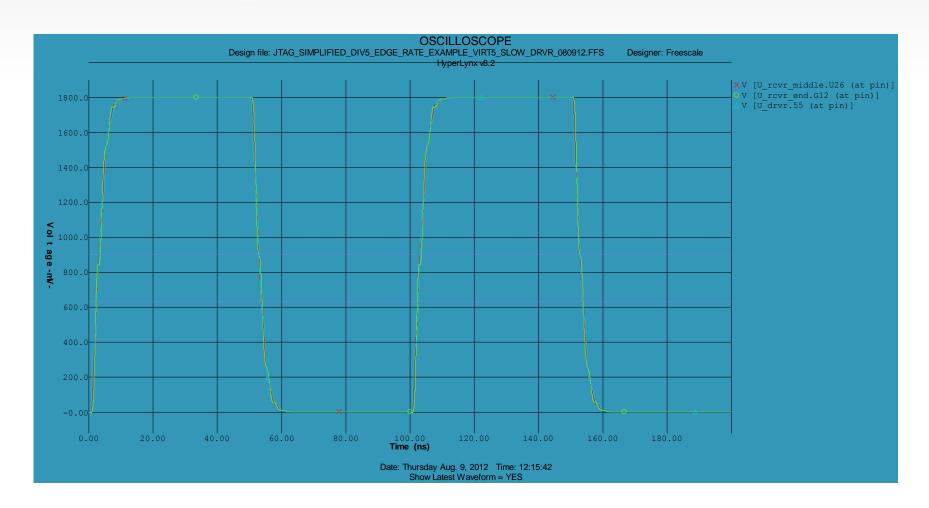

Design File: JTAG simplified dv5 edge rate evample virt2 slow dvr 080912ffs HyperLynx LineSmv8.2

#### **Shorten lengths: Slow Driver**

#### **Shorten lengths: Slow Driver**

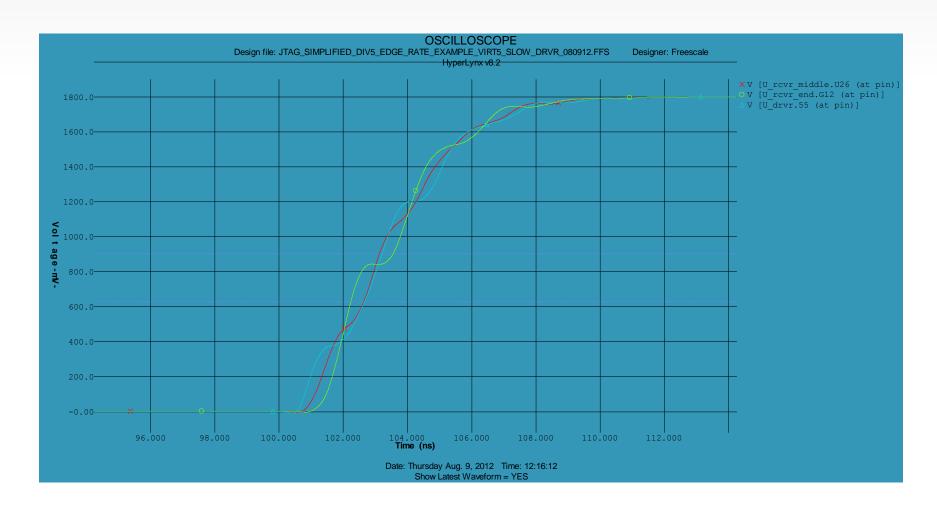

#### **Shorten lengths: Faster Slow Driver**

Design File: JTAG simplified dv5 edge rate example virt5 slow dvr 080912ffs HyperLynx LineSmv82

#### **Shorten lengths: Faster Slow Driver**

#### **Shorten lengths: Faster Slow Driver**

#### **Shorten lengths: Fast Driver**

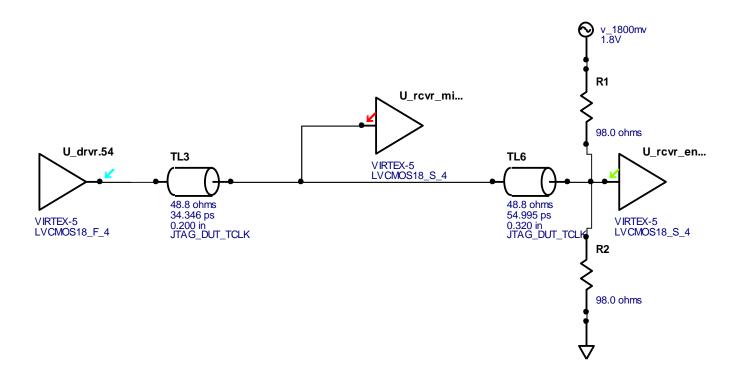

### norten lengths & Use Thevenin Termination: Fast Driver

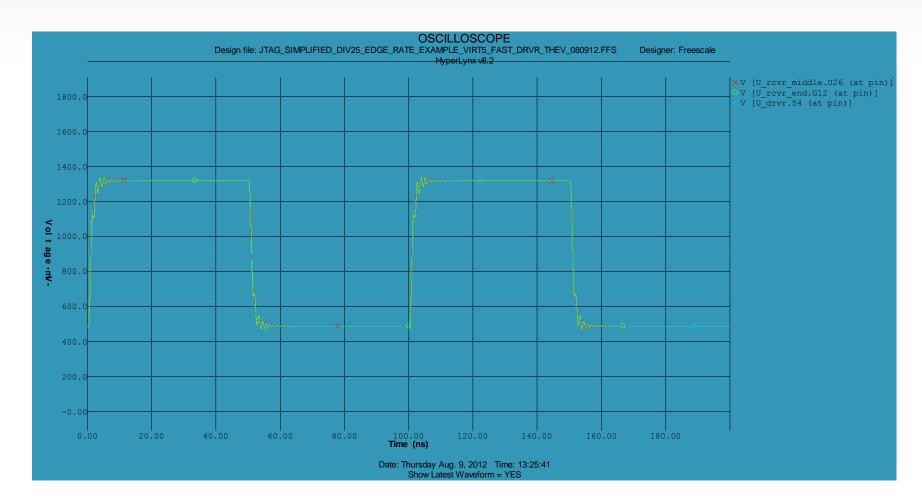

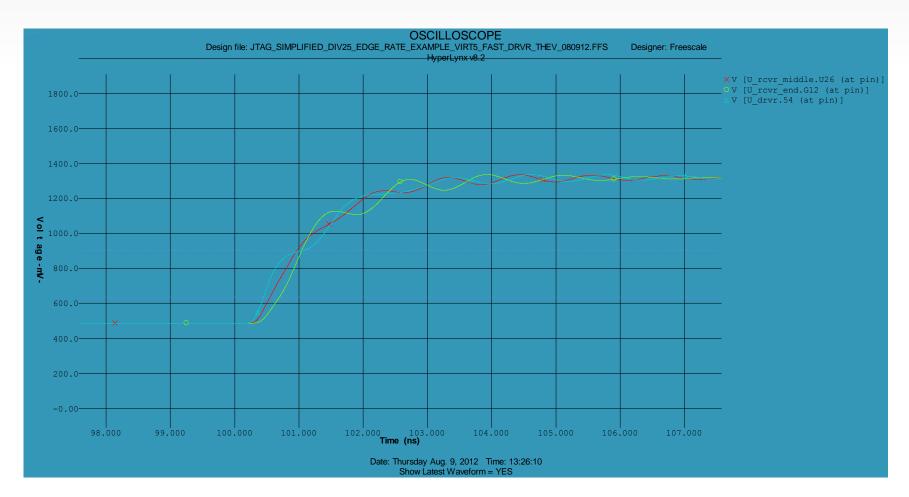

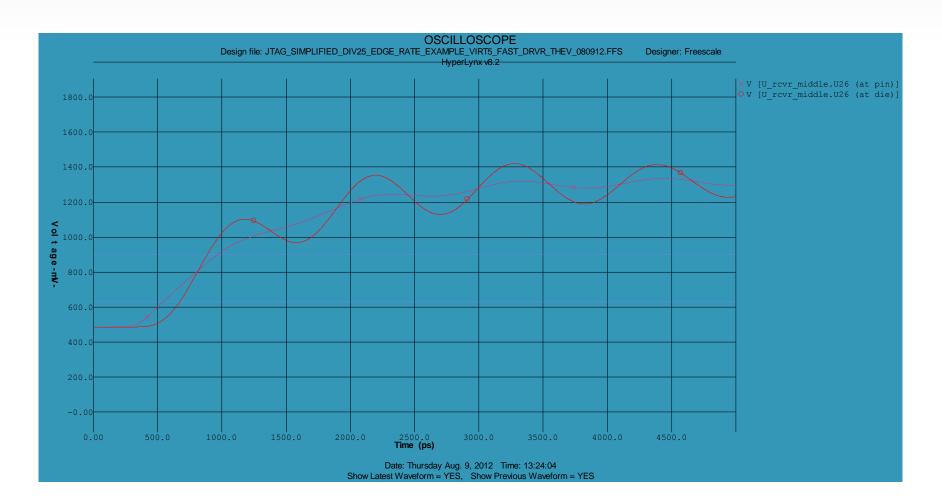

Design File: JTAG\_simplified\_dv25\_edge\_rate\_example\_virt5\_fast\_dvr\_thev\_080912ffs HyperLynxLineSmv82

### norten lengths & Use Thevenin Termination: Fast Driver

### Phorten lengths & Use Thevenin Termination: Fast Driver

### NP orten lengths & Use Thevenin Termination: Fast Driver

→ Edge is better but swing is too narrow with sampling point at ~ Ovdd/2

## Inorten lengths & use Thevenin Termination: Stronger Fast Driver

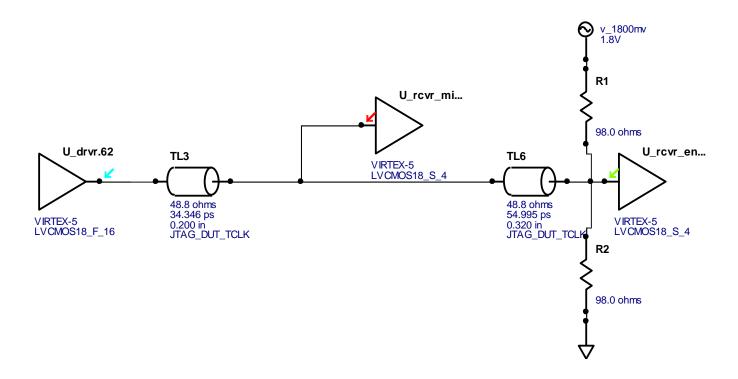

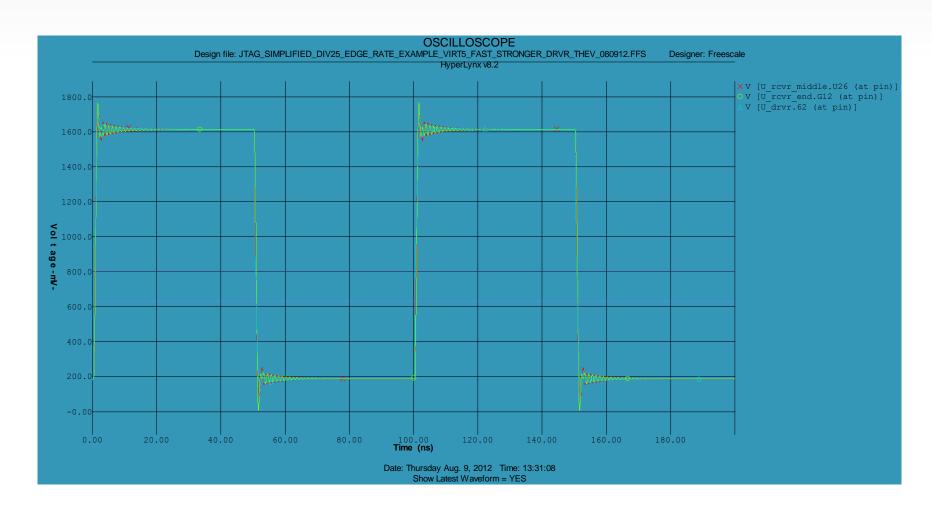

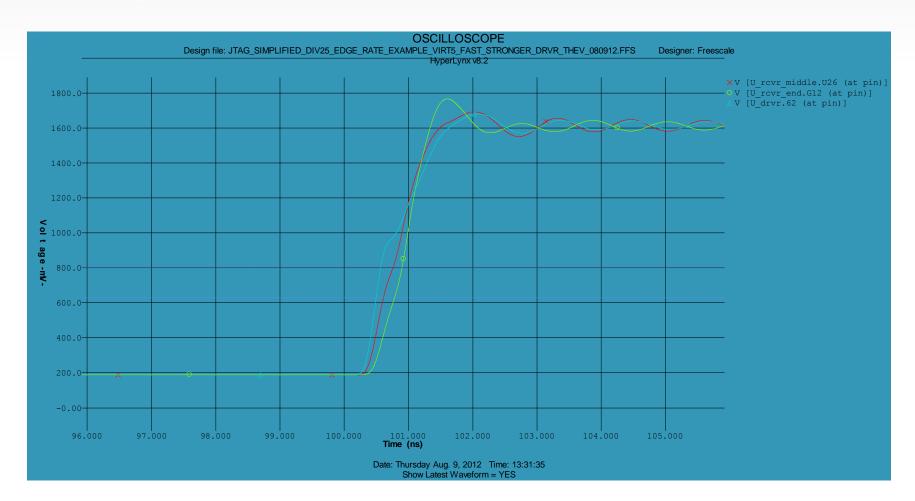

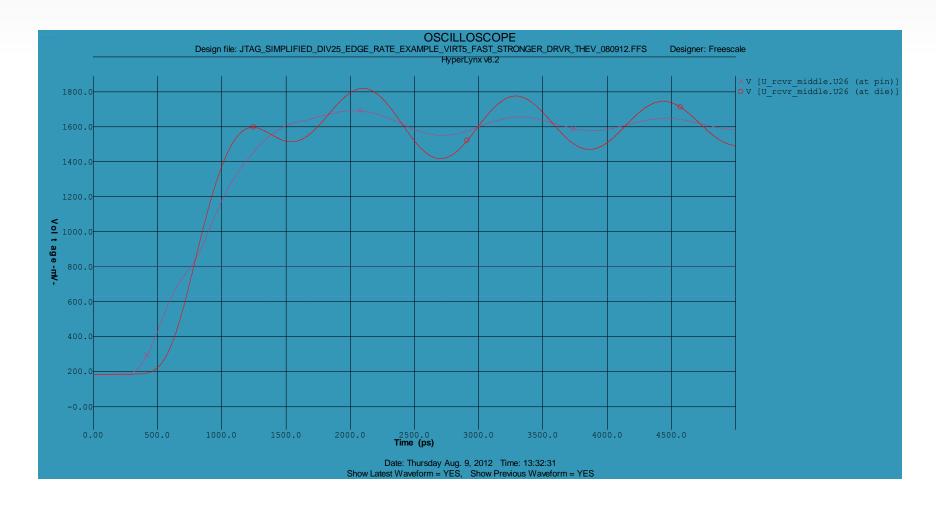

Design File: JTAG simplified\_dv25\_edge\_rate\_evample\_virt5\_fast\_stronger\_dvr\_thev\_080912ffs HyperLynxLineSmv82

# norten lengths & use Thevenin Termination: Stronger Fast Driver

### Chorten lengths & use Thevenin Termination: Stronger Fast Driver

### Inorten lengths & use Thevenin Termination: Stronger Fast Driver → Edge is good & Swing is good now

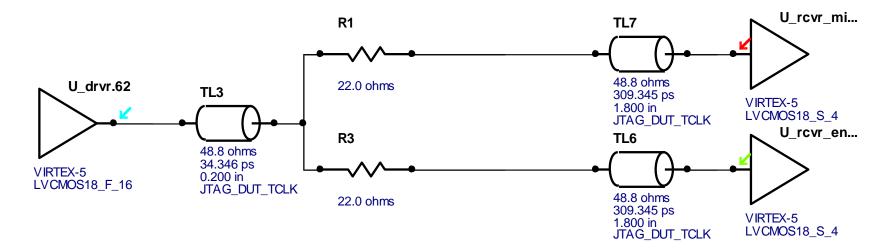

### Torten lengths & use Series Termination and Tee Route

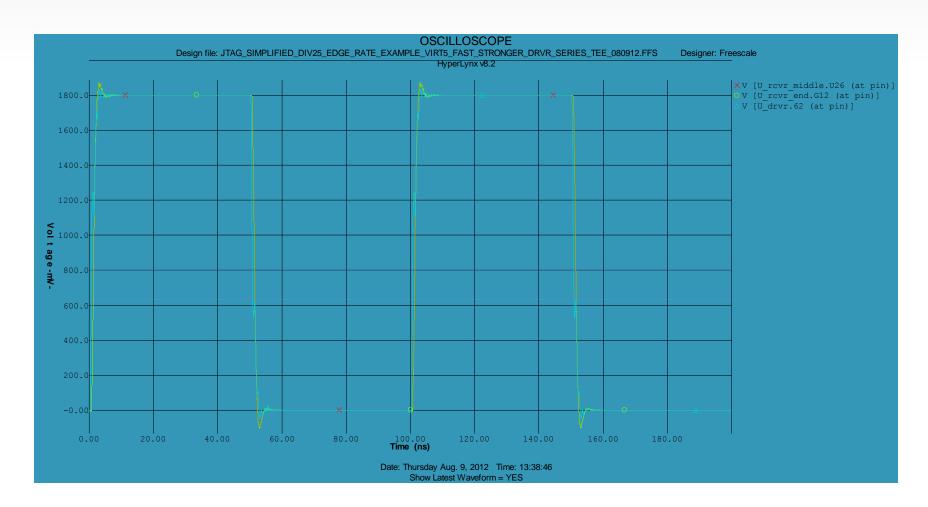

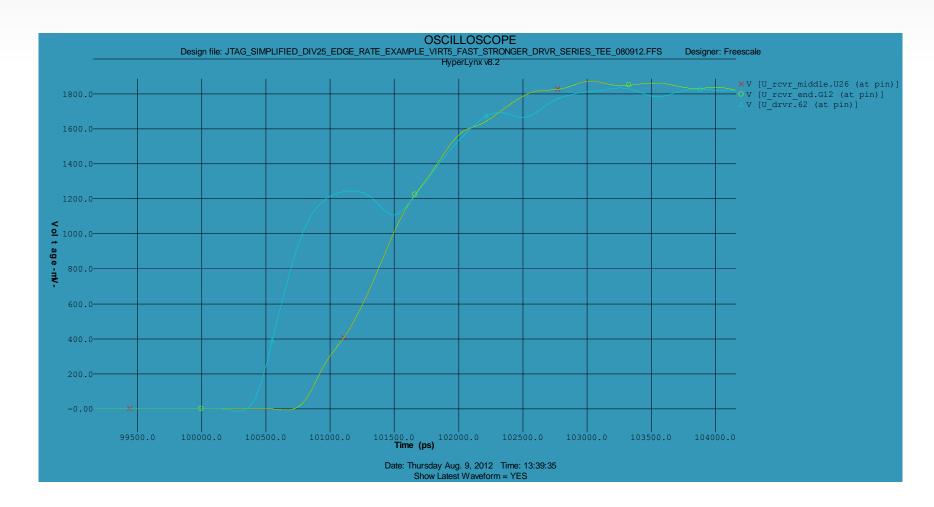

Design File: JTAG simplified\_dv25\_edge\_rate\_example\_virt5\_fast\_stronger\_dvr\_series\_tee\_080912ffs HyperLynxLineSimv82

### Chorten lengths & use Series Termination and Tee Route

### Chorten lengths & use Series Termination and Tee Route

### norten lengths & use Series Termination and Tee

Route: → Unequal Loads cause skew; be careful for timing

### 2) SYSCLK Input Edge Rate

Freescale, the Freescale logo, AltiVec, C-5, CodeTEST, CodeWarrior, ColdFire, ColdFire+, C-Ware, the Energy Efficient Solutions logo, Kinetis, mobileGT, PEG, PowerQUICC, Processor Expert, CorlO, Coriva, SafeAssure, the SafeAssure logo, StarCorr, Symphony and VortiCa are trademarks of Freescale Semiconductor, Inc., Reg. U.S. Pat. 8. Tm. Off. Airfast, Beekit, Beekit, BeeStack, CoreNet, Flexis, Layerscape, Magniy, MXC, Platform in a Package, OorlO Qonverge, QUICC Engine, Ready Play, SMARTMOS, Tower, TurbcLink, Vybrid and Xtrinsic are trademarks of Freescale Semiconductor, Inc. All other product or service names are the property of their respective owners. © 2013 Freescale Semiconductor, Inc.

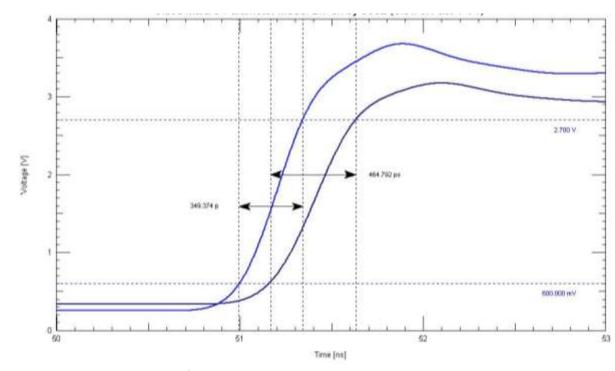

#### **SYSCLK Simulation**

- Simulate Various Clock Drivers

- Do the Clock Drivers meet the HW spec values for the SYSCLK spec?

- Look at Edge Rate at CPU.

- Look at Fast and Slow Corners for Clock Driver and CPU SYSCLK input from IBIS models.

# 3) Die vs Pin Probing for Read (incoming/receive) Waveforms

Freescale, the Freescale logo, AltiVec, C-5, CodeTEST, CodeWarrior, ColdFire, ColdFire+, C-Ware, the Energy Efficient Solutions logo, Kinetis, mobileGT, PEG, PowerQUICC, Processor Expert, Conf. Qorivay, SafeAssure, the SafeAssure logo, StarCore, Symphony and VortiQa are trademarks of Freescale Semiconductor, Inc., Reg. U.S. Pat. & Tm. Off. Airfast, Beeklit, Beeklitae, CoreNet, Flexis, Layerscape, MagniV, MXC, Platform in a Package, QorlQ Qonverge, QUICC Engine, Ready Play, SMARTMOS, Tower, TurboLink, Vybrid and Xtinsic are trademarks of Freescale Semiconductor, Inc. All other product or service names are the property of their respective owners. © 2013 Freescale Semiconductor, Inc.

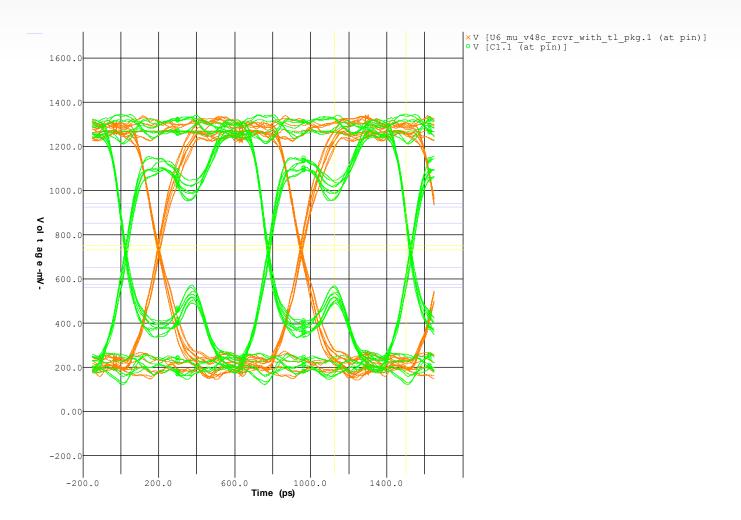

#### Signal Integrity FAQ: Die vs Pin Probing

- Especially an issue for signals into CPUs

- Large package sizes create longer transmission lines/delays

- Reflection from end of transmission line will distort signal not at end of transmission line

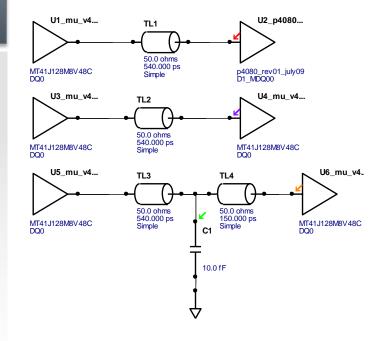

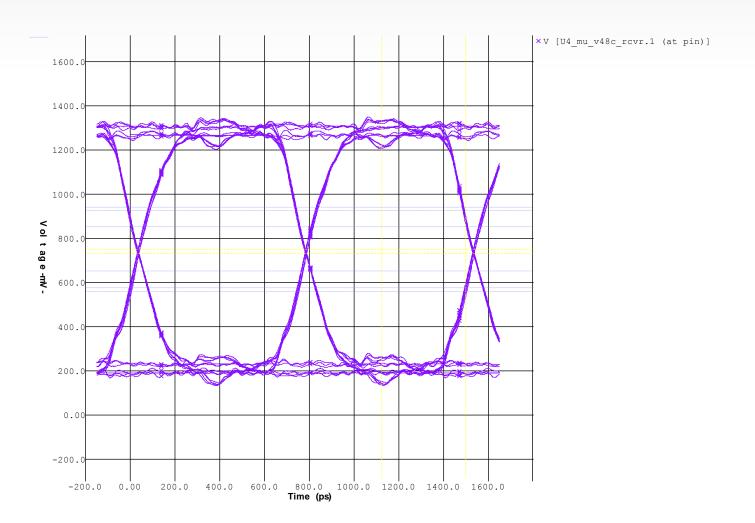

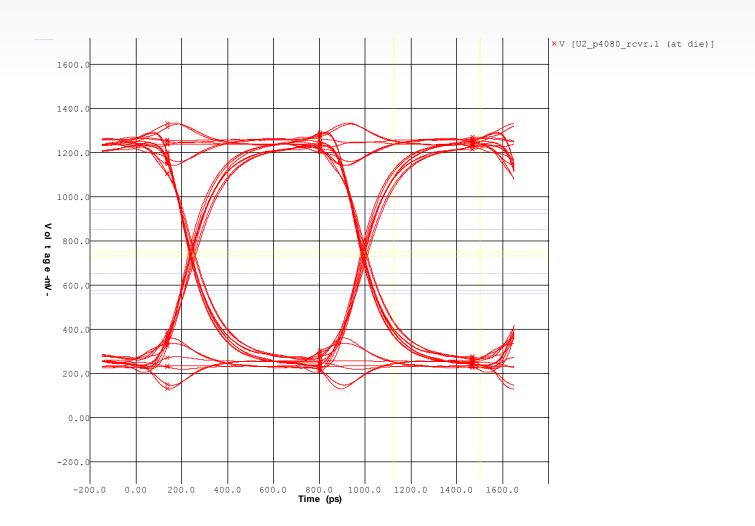

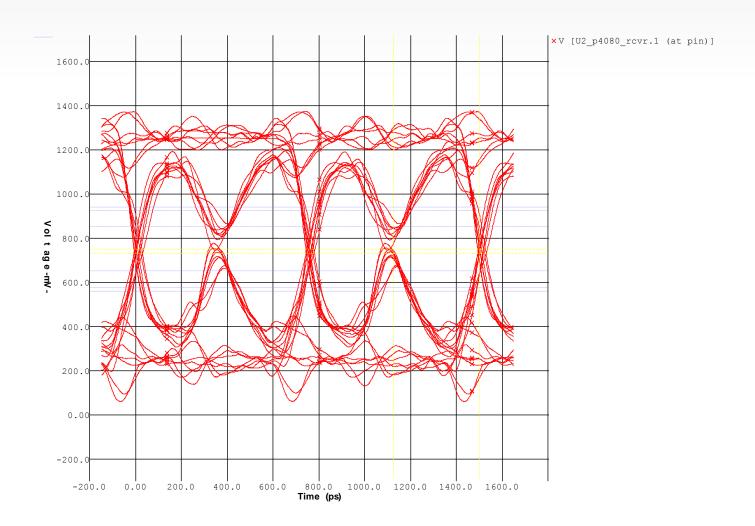

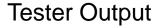

#### Die vs Pin Simulation Example

#### Die vs Pin

- Top is Memory to P4080

- Middle is Memory to Memory

- Bottom is Memory to Memory with probe point 150ps from end of net

- Purpose is to test effect of P4080 package probe point at pin vs die

- P4080 package electrical length is approx 150 ps

Design File: v48c\_to\_p4080\_053110.ffs HyperLynx LineSim V8.0

#### Read Waveform Measured at Memory Die

#### Read Waveform Measured at Memory Pin

#### Read Waveform Measured at P4080 Die

#### Read Waveform Measured at P4080 Pin

### Lead Waveform Measured at Memory Pin and 150 ps back from Memory Pin

### 4) DDR Read Measurement

Freescale, the Freescale logo, AltiVec, C-5, CodeTEST, CodeWarrior, ColdFire, ColdFire+, C-Ware, the Energy Efficient Solutions logo, Kinetis, mobileGT, PEG, PowerQUICC, Processor Expert, Corf.Q. Ordiva, SafeAssure, the SafeAssure logo, StarCorr, Symphony and VortiCa are trademarks of Freescale Semiconductor, Inc., Reg. U.S. Pat. 8. Tm. Off. Airlast, Beekit, Beekit, Beekitack, CoreNet, Flexis, Layerscape, MagniV, MXC, Platform in a Package, OorlQ Qonverge, QUICC Engine, Ready Play, SMARTMOS, Tower, TurbcLink, Vybrid and Xtrinsic are trademarks of Freescale Semiconductor, Inc. All other product or service names are the property of their respective owners. © 2013 Freescale Semiconductor, Inc.

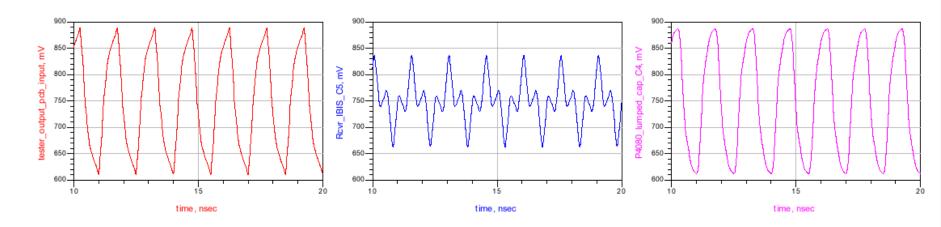

## For P4080 Receiver (No ODT) Inserted

Receiver at Pin/C5

Receiver at Die/C4

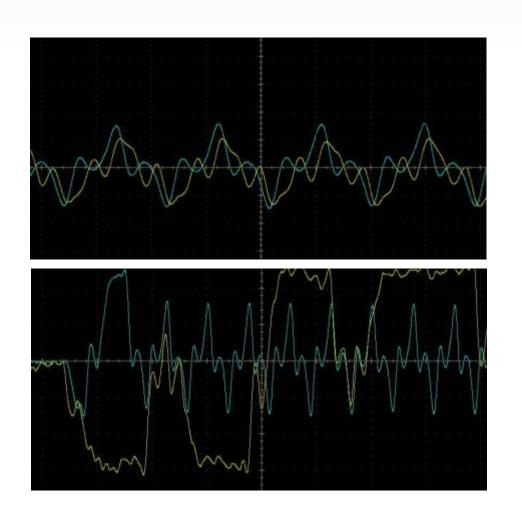

### >mpare No ODT Measurement vs Simulated (Pre-Tuned)

# 5) DDR3-1866 Write Timing for Two DIMM System

Freescale, the Freescale logo, AltiVec, C-5, CodeTEST, CodeWarrior, ColdFire, ColdFire+, C-Ware, the Energy Efficient Solutions logo, Kinetis, mobileGT, PEG, PowerQUICC, Processor Expert, Onfl., Ooriva, SafeAssure, the SafeAssure logo, StarCore, Symphony and VortiCa are trademarks of Freescale Semiconductor, Inc., Reg. U.S. Pat. & Tm. Off. Airfast, Beeklit, BeekStack, CoreNet, Flexis, Layerscape, MagniV, MXC, Platform in a Package, QorlQ Qonverge, QUICC Engine, Ready Play, SMARTMOS, Tower, TurboLink, Vybrid and Xirnisic are trademarks of Freescale Semiconductor, Inc. All other product or service names are the property of their respective owners. © 2013 Freescale Semiconductor, Inc.

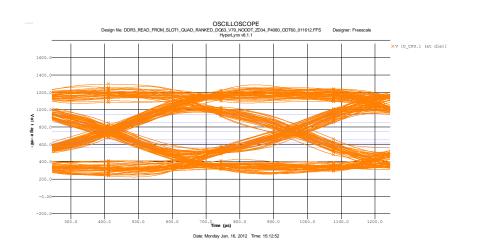

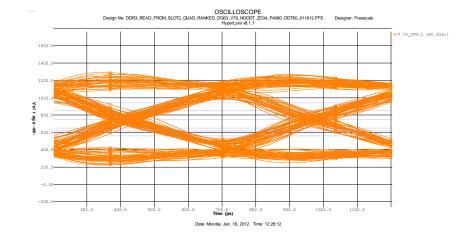

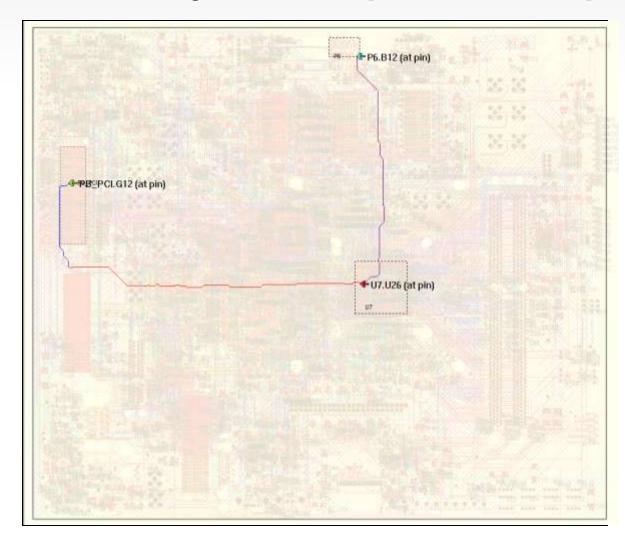

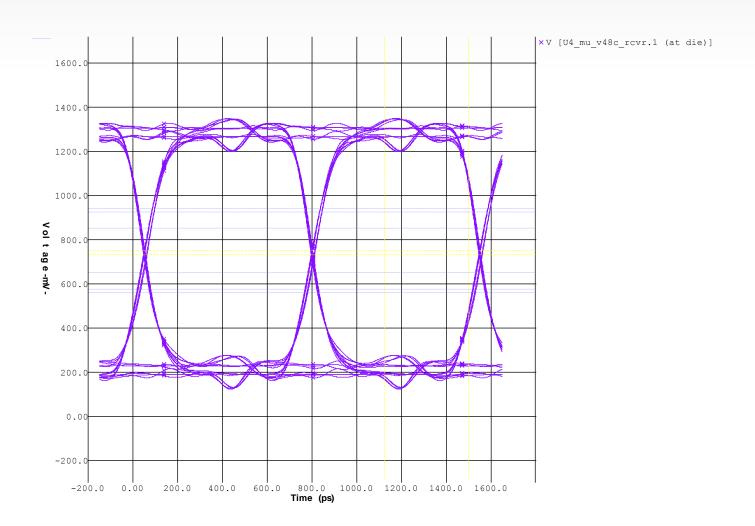

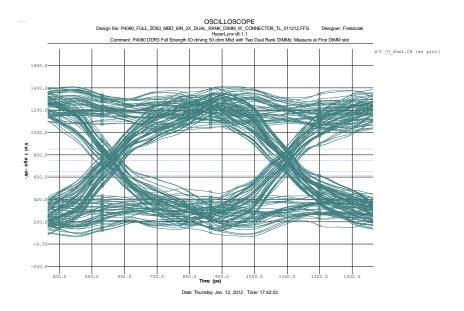

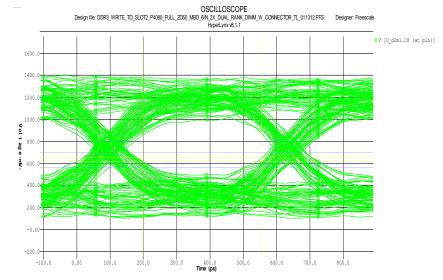

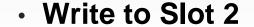

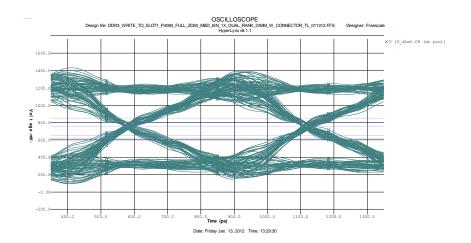

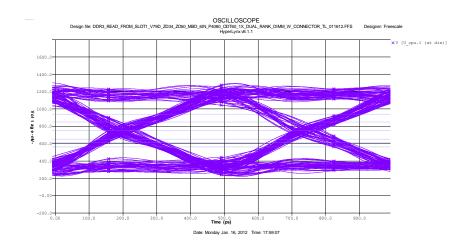

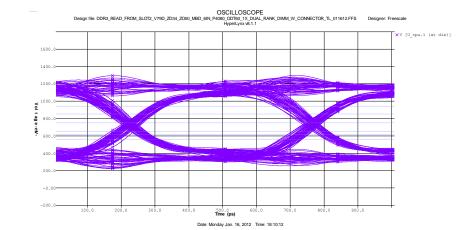

#### DDR3-1866 Dual and Quad Ranked DIMM Plots

- Goal is to look at DDR3 write waveforms for DDR3-1866 to see if first or second DIMM slot shows better signal integrity behavior

- Look at one dual-ranked, two dual-ranked, one quad-ranked DIMM options

- PCB is based on T4 QDS preliminary layout

- 50 ohm PCB

- 6 inch trace from CPU to first DIMM

- IO buffer models for CPU are P4080 and are not T4-based

- Comments:

- A single dual-ranked DIMM shows improvement for using the second slot of two slots (farthest from CPU).

- Two Dual Ranked or one Quad Ranked DIMM does not show as strong of a preference for first or second DIMM location from this set of simulations (with non-T4 models).

### Lata Eye Width vs Number and Type of DIMMs (Typ PVT) – Greater Numbers are better

| Read/Write | DIMM      | #_DIMMs | Slot | Data Eye Width at AC-<br>DC Vin Levels (Ave<br>High & Low Vin - ps) |

|------------|-----------|---------|------|---------------------------------------------------------------------|

| Write      | Dual Rank | 1       | 2    | 426                                                                 |

| Read       | Dual Rank | 1       | 2    | 399.5                                                               |

| Read       | Dual Rank | 2       | 2    | 354.5                                                               |

| Read       | Dual Rank | 2       | 1    | 351                                                                 |

| Write      | Dual Rank | 2       | 2    | 350.5                                                               |

| Write      | Dual Rank | 2       | 1    | 346.5                                                               |

| Write      | Quad Rank | 1       | 2    | 334                                                                 |

| Write      | Dual Rank | 1       | 1    | 332                                                                 |

| Read       | Dual Rank | 1       | 1    | 305.5                                                               |

| Write      | Quad Rank | 1       | 1    | 285.5                                                               |

| Read       | Quad Rank | 1       | 2    | 234.5                                                               |

| Read       | Quad Rank | 1       | 1    | 234                                                                 |

### Lata Eye Width vs Number and Type of DIMMs (Slow PVT) – Greater Numbers are better

| Read/Write | DIMM      | #_DIMMs | Slot | Data Eye Width at AC-<br>DC Vin Levels (Ave<br>High & Low Vin - ps) |

|------------|-----------|---------|------|---------------------------------------------------------------------|

| Write      | Dual Rank | 1       | 2    | 406.5                                                               |

| Read       | Dual Rank | 1       | 2    | 359                                                                 |

| Write      | Dual Rank | 2       | 2    | 321                                                                 |

| Write      | Dual Rank | 1       | 1    | 309.5                                                               |

| Write      | Dual Rank | 2       | 1    | 307.5                                                               |

| Write      | Quad Rank | 1       | 2    | 299                                                                 |

| Read       | Dual Rank | 1       | 1    | 295.5                                                               |

| Read       | Dual Rank | 2       | 2    | 283                                                                 |

| Write      | Quad Rank | 1       | 1    | 250                                                                 |

| Read       | Dual Rank | 2       | 1    | 247                                                                 |

| Read       | Quad Rank | 1       | 1    | 196.5                                                               |

| Read       | Quad Rank | 1       | 2    | 177                                                                 |

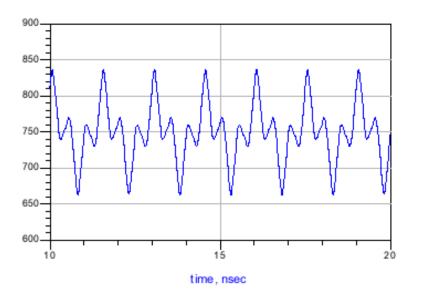

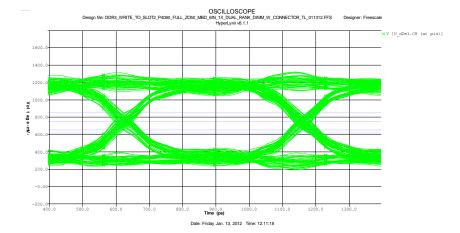

#### DDR3-1866 Write with Two Dual Ranked DIMMs

Write to Slot 1

#### Write to Slot 2

### DR3-1866 Write with One Dual Ranked DIMM:

#### Improvement in Data Eye is More Pronounced

Write to Slot 1

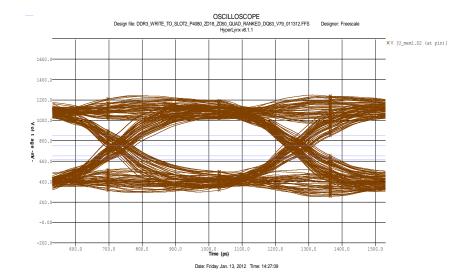

#### DDR3-1866 Write with One Quad Ranked DIMM

Write to Slot 1

#### DDR3-1866 Read with Two Dual Ranked DIMMs

Read from Slot 1

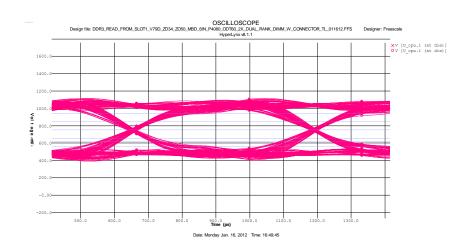

#### DDR3-1866 Read with One Dual Ranked DIMM

Read from Slot 1

Read from Slot 2

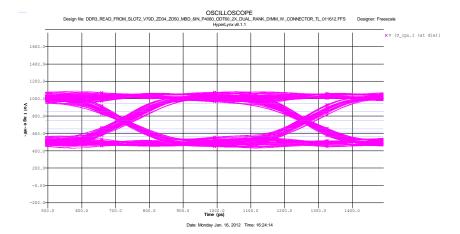

#### DDR3-1866 Read with One Quad Ranked DIMM

Read from Slot 1

Read from Slot 2