| © FREESCALE SEMICONDUCTOR, INC. ALL RIGHTS RESERVED. |          |                          | PRINT VERSION NOT TO SCALE |             |

|------------------------------------------------------|----------|--------------------------|----------------------------|-------------|

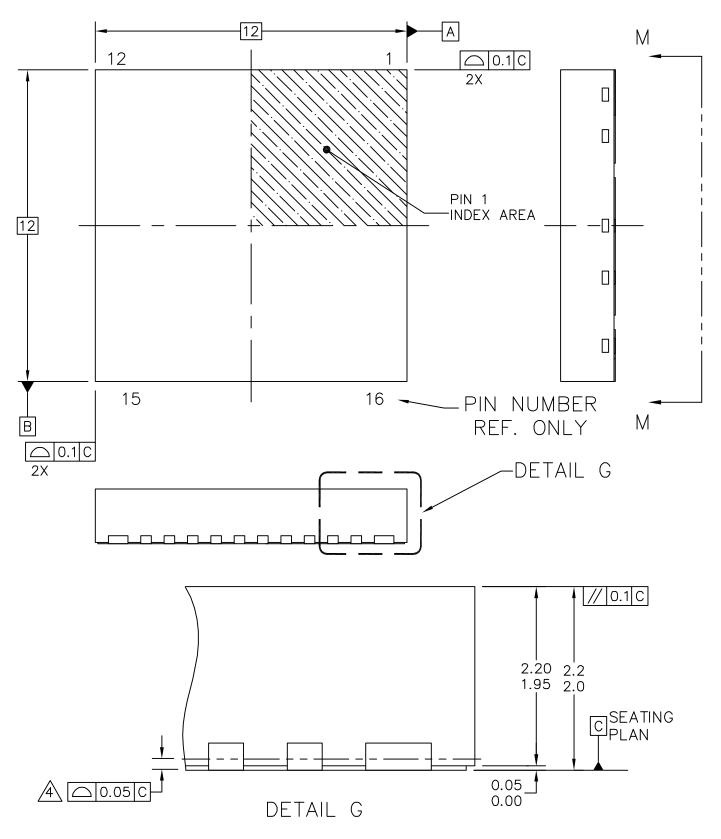

| TITLE: POWER QUAD FLAT                               |          | DOCUMENT NO: 98ARL10521D |                            | REV: D      |

| NON-LEADED PACKAGE (PWR QFN)                         |          | CASE NUMBER              | : 1402–03                  | 21 SEP 2011 |

| 16 TERMINAL, 0.9 PITCH(12X12                         | 2X2.1) [ | STANDARD: NON-JEDEC      |                            |             |

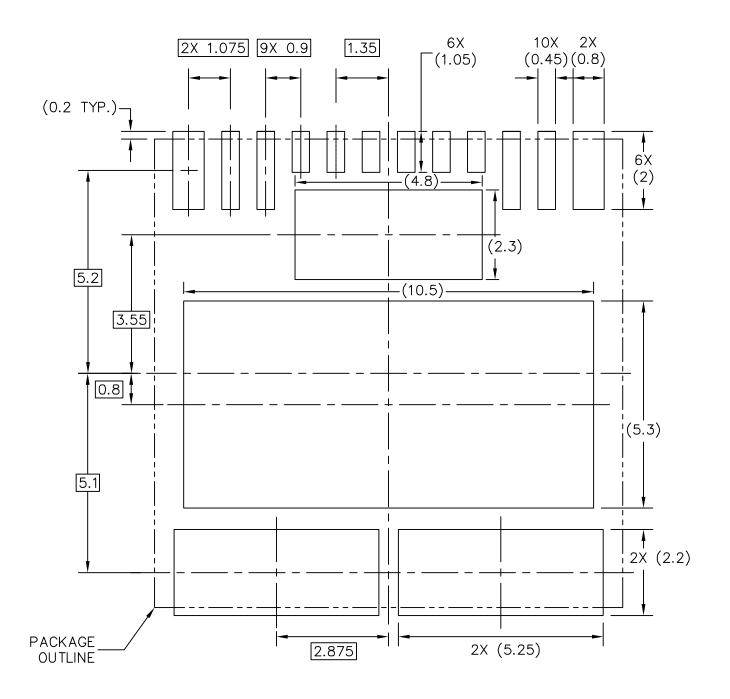

VIEW M-M

| FREESCALE SEMICONDUCTOR, INC. ALL RIGHTS RESERVED. | MECHANICAL OUTLINE |                          | PRINT VERSION NOT TO SCALE |             |

|----------------------------------------------------|--------------------|--------------------------|----------------------------|-------------|

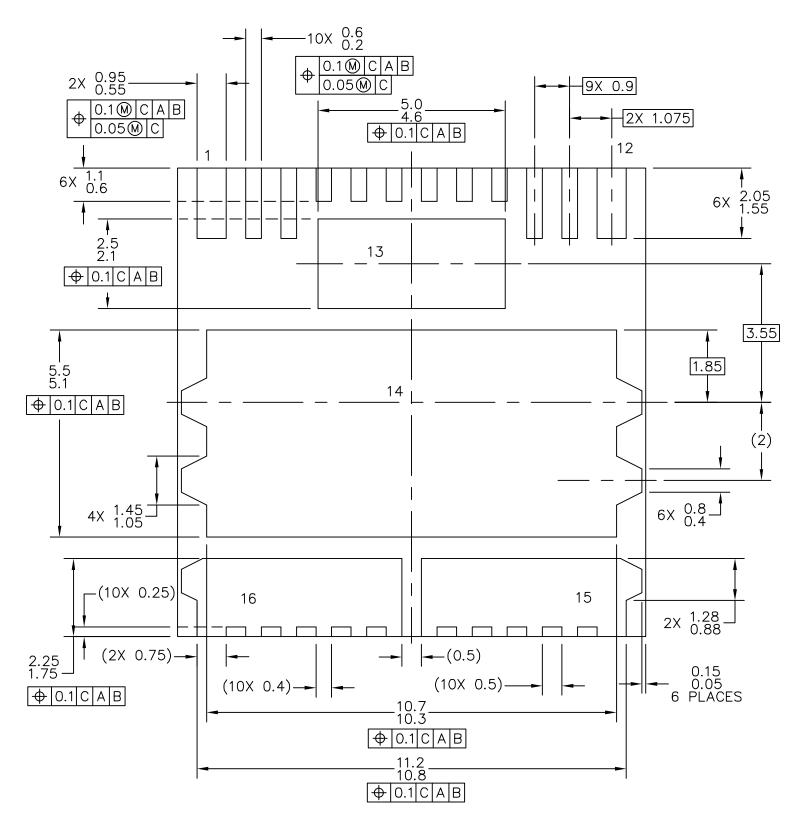

| TITLE: POWER QUAD FLAT                             |                    | DOCUMENT NO: 98ARL10521D |                            | REV: D      |

| NON-LEADED PACKAGE (PWR QFN)                       |                    |                          |                            | 21 SEP 2011 |

| 16 TERMINAL, 0.9 PITCH(1                           | 2X12X2.1)          | STANDARD: NO             | N-JEDEC                    |             |

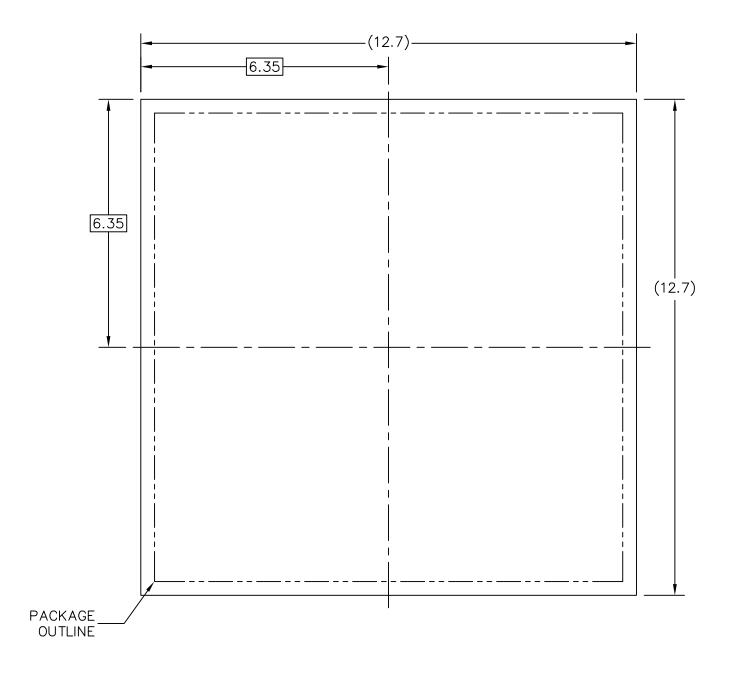

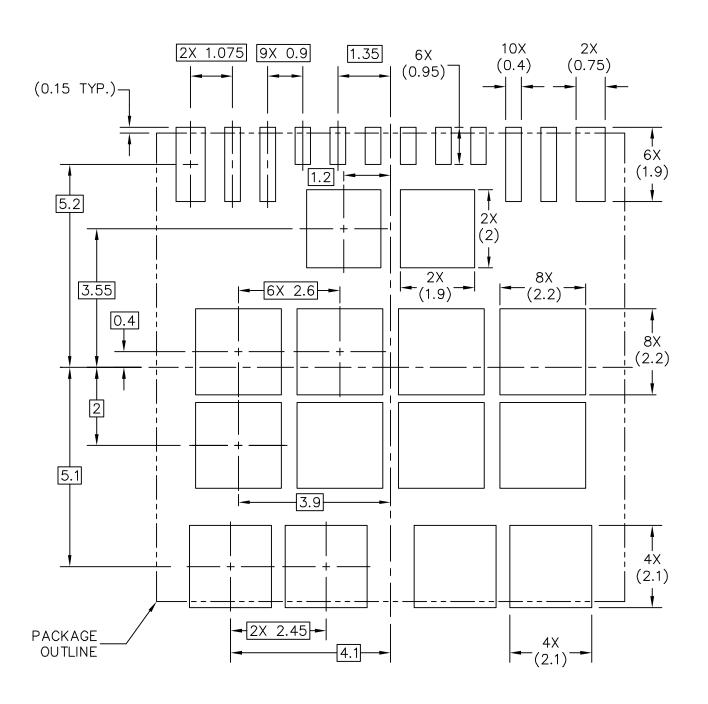

PCB DESIGN GUIDELINES - SOLDER MASK OPENING PATTERN 1

| © FREESCALE SEMICONDUCTOR, INC. ALL RIGHTS RESERVED. | MECHANICAL OUTLINE |              | PRINT VERSION NOT TO SCALE |             |

|------------------------------------------------------|--------------------|--------------|----------------------------|-------------|

| TITLE: POWER QUAD FLAT                               |                    | DOCUMENT NO  | ): 98ARL10521D             | REV: D      |

| NON-LEADED PACKAGE (PWR QFN)                         |                    | CASE NUMBER  | : 1402–03                  | 21 SEP 2011 |

| 16 TERMINAL, 0.9 PITCH(12X12X2.1)                    |                    | STANDARD: NO | N-JEDEC                    |             |

PCB DESIGN GUIDELINES - SOLDER MASK OPENING PATTERN 2

| FREESCALE SEMICONDUCTOR, INC. ALL RIGHTS RESERVED. | MECHANICAL OUTLINE |                          | PRINT VERSION NOT TO SCALE |             |

|----------------------------------------------------|--------------------|--------------------------|----------------------------|-------------|

| TITLE: POWER QUAD FLAT                             |                    | DOCUMENT NO: 98ARL10521D |                            | REV: D      |

| NON-LEADED PACKAGE (PWR QFN)                       |                    |                          |                            | 21 SEP 2011 |

| 16 TERMINAL, 0.9 PITCH(1                           | 2X12X2.1)          | STANDARD: NO             | N-JEDEC                    |             |

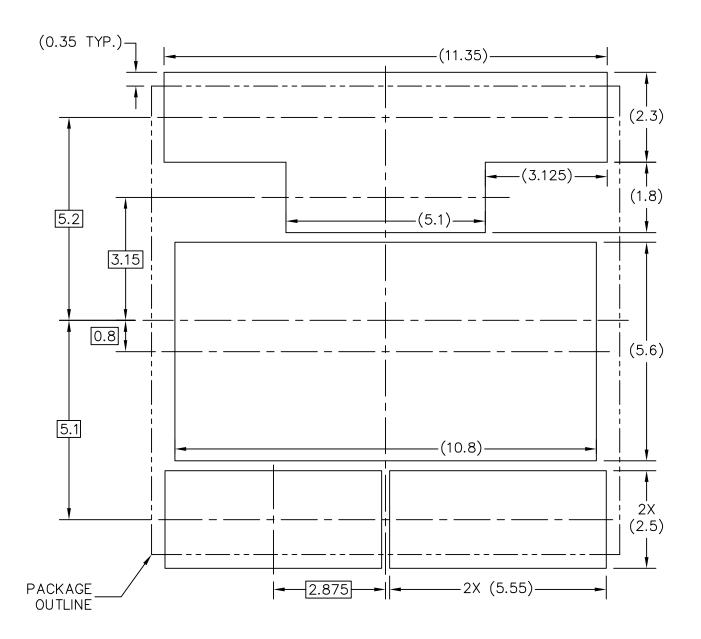

PCB CU GUIDELINES - I/O PADS & SOLDERABLE AREAS

| FREESCALE SEMICONDUCTOR, INC. ALL RIGHTS RESERVED. | MECHANICAL OUTLINE |                          | PRINT VERSION NOT TO SCALE |             |

|----------------------------------------------------|--------------------|--------------------------|----------------------------|-------------|

| TITLE: POWER QUAD FLAT                             |                    | DOCUMENT NO: 98ARL10521D |                            | REV: D      |

| NON-LEADED PACKAGE (PWR QFN)                       |                    |                          |                            | 21 SEP 2011 |

| 16 TERMINAL, 0.9 PITCH(1                           | 2X12X2.1)          | STANDARD: NO             | N-JEDEC                    |             |

SOLDER PASTE STENCIL GUIDELINES

| FREESCALE SEMICONDUCTOR, INC. ALL RIGHTS RESERVED. | MECHANICAL OUTLINE |                          | PRINT VERSION NOT TO SCALE |             |

|----------------------------------------------------|--------------------|--------------------------|----------------------------|-------------|

| TITLE: POWER QUAD FLAT                             |                    | DOCUMENT NO: 98ARL10521D |                            | REV: D      |

| NON-LEADED PACKAGE (PWR QFN)                       |                    |                          |                            | 21 SEP 2011 |

| 16 TERMINAL, 0.9 PITCH(1                           | 2X12X2.1)          | STANDARD: NO             | N-JEDEC                    |             |

## NOTES:

- 1. ALL DIMENSIONS ARE IN MILLIMETERS.

- 2. DIMENSIONING AND TOLERANCING PER ASME Y14.5M-1994.

- 3. THE COMPLETE JEDEC DESIGNATOR FOR THIS PACKAGE IS: HF-PQFP-N.

- 4. COPLANARITY APPLIES TO LEADS AND CORNER LEADS.

- 5. MINIMUM METAL GAP SHOULD BE 0.25MM.

| © FREESCALE SEMICONDUCTOR, INC. ALL RIGHTS RESERVED.  MECHANICAL OUTLINE |                  | PRINT VERSION NO         | T TO SCALE  |

|--------------------------------------------------------------------------|------------------|--------------------------|-------------|

| TITLE: POWER QUAD FLAT                                                   | DOCUMENT N       | DOCUMENT NO: 98ARL10521D |             |

| NON-LEADED PACKAGE (PWR QF                                               | · 1              | R: 1402-03               | 21 SEP 2011 |

| 16 TERMINAL, 0.9 PITCH(12X12X2                                           | 2.1) STANDARD: N | ) STANDARD: NON-JEDEC    |             |