#### **NXP Semiconductors**

Data Sheet: Technical Data

### **RF112**

# **RF112 Transceiver Data Sheet**

#### **Features**

- Zero I/F operation in 2.4GHz (2.4-2.5GHz) Low and 5GHz (4.9-6GHz) High Industrial, Scientific, and Medical (ISM) Bands

- Three independently operating RF sub-systems.

- One dual band 1x2 MIMO transceiver, TRX

- One dual band observation receiver, RO1

- One high band observation receiver, RO2

- Aggregate support for 1x Transmit, 4x Receive antenna operation

- · Receiver features

- Direct conversion, low noise and high dynamic range receive chain

- High speed AGC interface (RSSI detector and RX gain control) to baseband

- Analog baseband filters (20, 40 and 80 MHz modulation bandwidth) with on-chip calibration

- Analog differential I/Q interface to baseband IC

- Transmitter features

- Direct conversion with adjustable gain transmit chain

- Analog baseband filter (20, 40 and 80 MHz modulation bandwidth) with on-chip calibration

- Analog differential I/Q interface to baseband

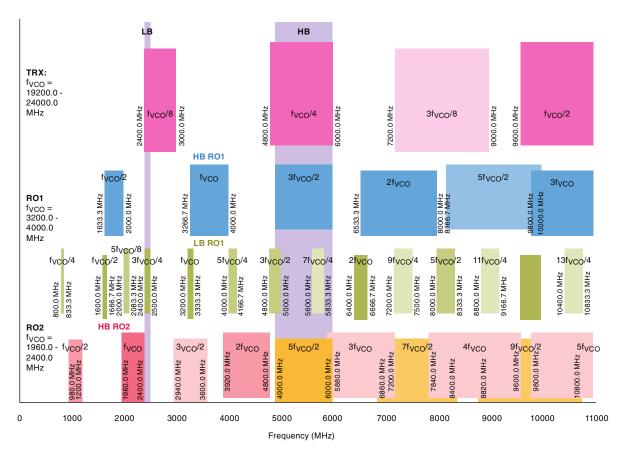

- Flexible frequency generation system

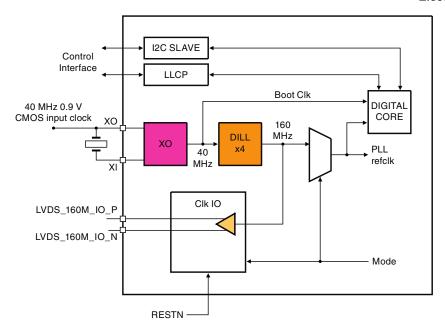

- 40 MHz crystal or external oscillator for frequency reference

- Adjustable crystal load to tune for minimum frequency error

- 4X multiplied input reference that can be routed to an output differential pair to be used as a low jitter 160 MHz reference by other devices in the system

- Independent synthesizers for each sub-system driven by a common reference

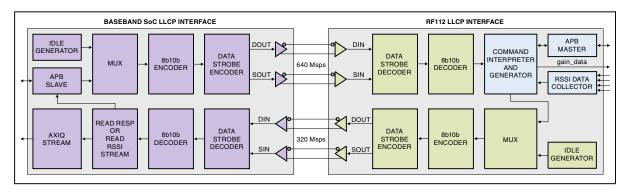

- Two interfaces for configuration and bi-directional data exchanges with the baseband IC

- A low complexity high-speed custom LVDS bus (LLCP)

- A traditional low-speed I2C bus

- Programmable digital core for transceiver control and calibration

- Auxiliary ADC support for calibration and external functions (voltage and temperature measurements)

- 64 pin QFN package

# **Table of Contents**

| 1 | Intro | duction                               | 3   |

|---|-------|---------------------------------------|-----|

| 2 | Pin a | assignments                           | 7   |

|   | 2.1   | RF112 transceiver QFN layout diagrams | 7   |

|   | 2.2   | Pinout list                           | 7   |

| 3 | Elec  | trical characteristics                | .11 |

|   | 3.1   | Overall DC electrical characteristics | 11  |

|   | 3.2   | General specification.                | 15  |

|   | 3.3   | Receiver specification.               | .15 |

|   | 3.4   | Transmitter specification             | 20  |

|   | 3.5   | Isolation.                            | 28  |

|   | 3.6   | Frequency generation specification    | 29  |

|   | 5.7  | Digital interface                    | 5  |

|---|------|--------------------------------------|----|

|   | 3.8  | Device start-up                      | 37 |

|   | 3.9  | Specification of auxiliary functions | 38 |

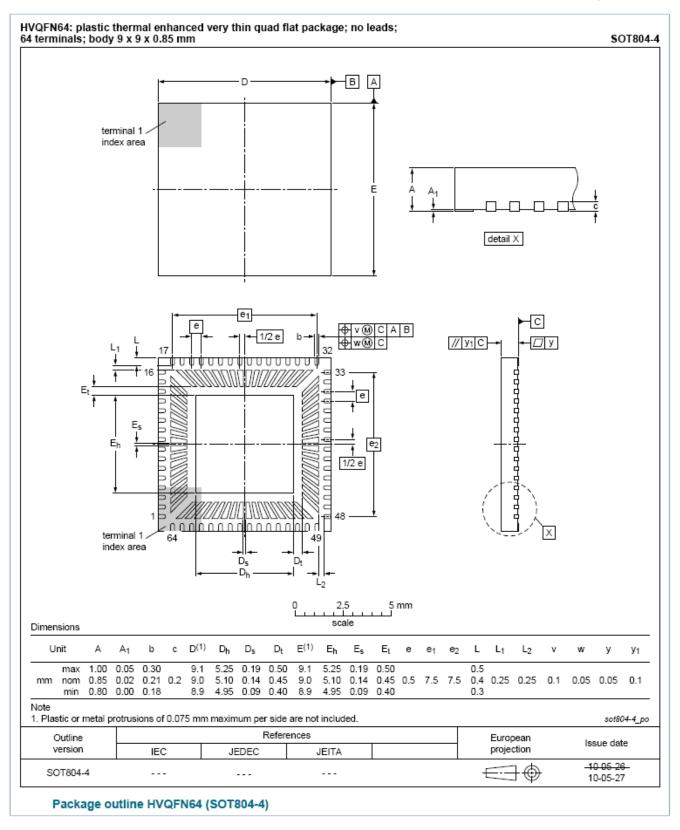

| 4 | Pack | tage information                     | 39 |

|   | 4.1  | Mechanical dimensions                | 39 |

| 5 | Orde | erable part information              | 42 |

| 6 | App  | lication                             | 42 |

|   | 6.1  | External components                  | 42 |

|   | 6.2  | PCB design.                          | 42 |

| 7 | Revi | ision history                        | 44 |

|   |      |                                      |    |

### 1 Introduction

The purpose and scope of this document is to provide the specifications for the RF112 1x4 ISM transceiver.

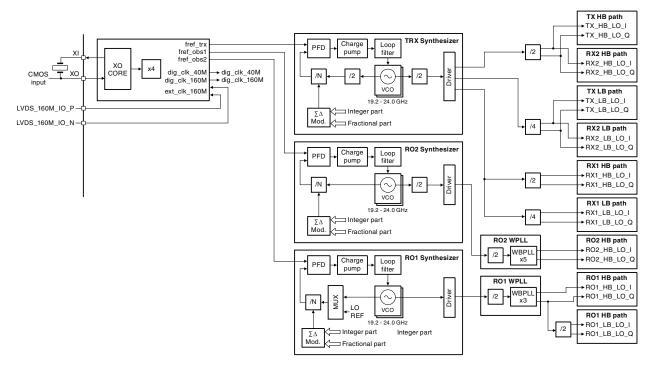

The RF112 Transceiver consists of three RF sub-systems; one dual band 1x2 MIMO transceiver, denoted TRX, one dual band observation receiver, denoted RO1, and one high band observation receiver, denoted RO2, together with a crystal oscillator and a digital core which is used to control the transceiver, and interfaces. The TRX, RO1, and RO2 sub-systems operate independently. The dual band units can be configured to work in either low band or high band, but since they share synthesizer, channel filters and analog baseband interfaces the bands cannot be used concurrently.

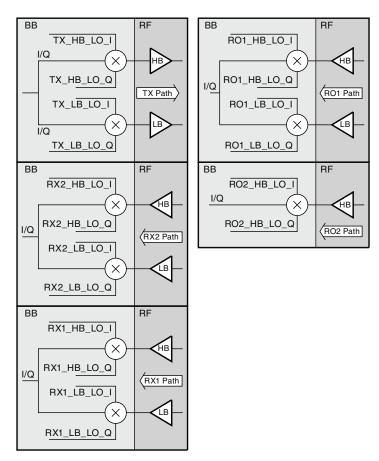

Figure 1. RF112 Transceiver Simplified model

The RF112 Transceiver uses a direct conversion architecture for both RX and TX. The chip has independent synthesizers for each sub-system driven from a common reference. The frequency reference can be a 40 MHz crystal or external oscillator. The input reference is multiplied internally by 4 and can be routed to an output differential driver for use as a low jitter 160 MHz frequency reference by other devices in the system. The

#### Introduction

gain in receive mode should be controlled by the baseband IC. The receive chain has low noise and high dynamic range. The analog baseband filters have on-chip calibration and supports 20, 40, or 80 MHz modulation bandwidth. An internal crystal oscillator is implemented to enable usage of a low cost crystal. The reference frequency can be fine-tuned to minimize the frequency error. A LVDS clock output is included to provide a reference clock to the baseband chip. An auxiliary ADC is implemented for calibration purposes and to serve various external functions like power and temperature measurements.

The two interfaces, a traditional low-speed I2C, and a low complexity high-speed custom LVDS buses are available for configuration and bi-directional data exchanges with the baseband. The high-speed LLCP interface can be used to provide a continuous stream of RF envelope detector samples after the LNA in each receiver chain. This allows the receiver AGC algorithm, located on the baseband chip, to observe the wideband signal level and optimize the receiver gain for best performance. The interface allows quick updates of the transmitter and receiver gains.

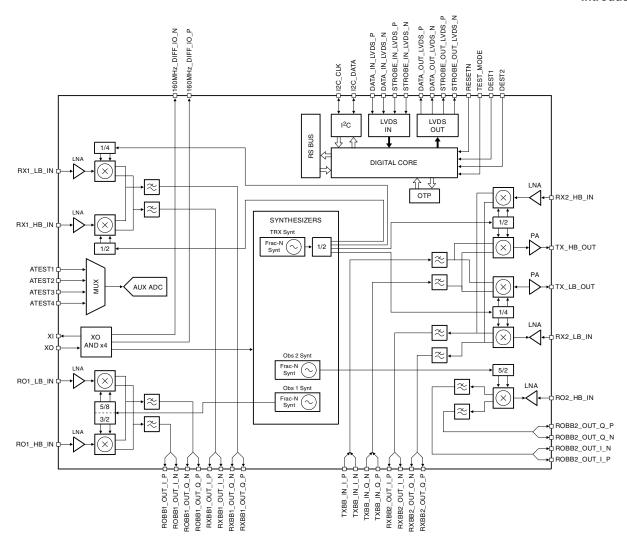

This figure shows top level block diagram of the RF112 Transceiver.

Figure 2. RF112 Transceiver block diagram

The TRX sub-system is capable of operating in TDD mode in either high band or low band. The TRX consists of one high band transceiver and one low band transceiver which share baseband filters and analog interfaces. The transceivers each have one transmitter and two identical receivers, the transmitter and one of the receivers share the same LO, the second receiver LO-phases are generated independently from the same synthesizer as the transmit-receive-pair. The LO generation for the TRX sub-system is kept running all the time, to keep the LO-phase relations fixed after chip power-on.

The observation receiver chains are identical to the main receive chains, but they have their own completely independent synthesizers. The two RO1 receivers (LB and HB) share synthesizer and baseband, and can, hence, not be used concurrently. The observation receiver synthesizers are kept running all the time.

The TRX receivers and the two observation receivers can be run at exactly the same LO frequency, so that the transceiver can be used in 1x3 Low Band or 1x4 MIMO High Band configuration, but with reduced performance.

#### Introduction

The analog filter bandwidths of the two TRX receivers are always the same. However, the bandwidth selection of the receivers and transmitters are completely independent. The bandwidth setting of the observation receivers are independent of both the TRX receivers and transmitters and of the other observation receiver.

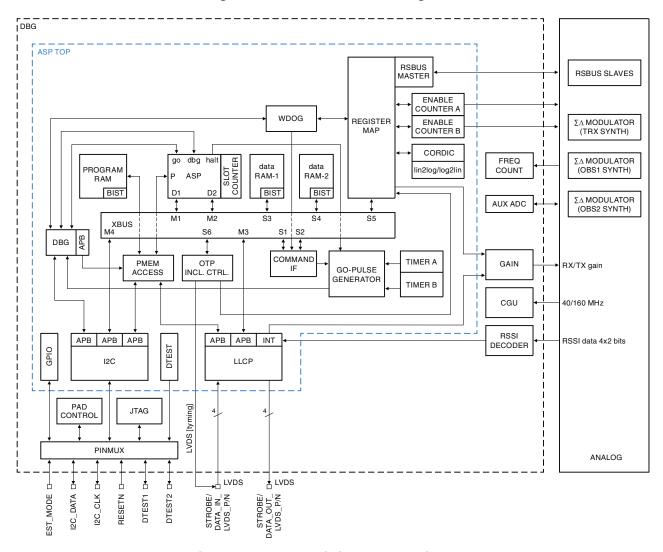

Below is the RF112 block diagram of the Transceiver digital controller:

Figure 3. RF112 Digital Block Diagram

The digital part of RF112 consists of an ASP and a number of digital hardware blocks, and interfaces both with the analogue part - via an RS bus, signals, and clocks - and with the outside world - via LLCP and I2C interfaces. The internal clock frequency is 160 MHz in normal operation, during boot a 40 MHz clock is used. The digital part is used to control and calibrate the analog part of the chip, both RF and baseband signal interfaces are analog.

### 2 Pin assignments

### 2.1 RF112 transceiver QFN layout diagrams

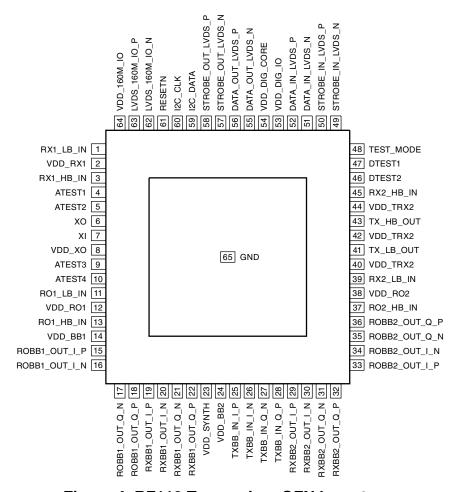

This figure shows the complete view of the RF112 QFN diagram.

Figure 4. RF112 Transceiver QFN layout

## 2.2 Pinout list

This table provides the pinout listing for the RF112 Transceiver by bus.

Table 1. Pinout list by bus

| Signal            | Signal description                                                    | Package       | Pin  | Power supply             | Notes |

|-------------------|-----------------------------------------------------------------------|---------------|------|--------------------------|-------|

| Signal            | Signal description                                                    | pin<br>number | type | Power suppry             | Notes |

|                   | Digital core l                                                        | VDS           |      | •                        |       |

| DATA_IN_LVDS_N    | Data in negative                                                      | 51            | I    | V <sub>DD</sub> _DIG_IO  | 1     |

| DATA_IN_LVDS_P    | Data in positive                                                      | 52            | I    | V <sub>DD</sub> _DIG_IO  | 1     |

| STROBE_IN_LVDS_N  | Data in strobe negative                                               | 49            | Ι    | V <sub>DD</sub> _DIG_IO  | 1     |

| STROBE_IN_LVDS_P  | Data in strobe positive                                               | 50            | _    | V <sub>DD</sub> _DIG_IO  | 1     |

| DATA_OUT_LVDS_N   | Data out negative                                                     | 55            | 0    | V <sub>DD</sub> _DIG_IO  |       |

| DATA_OUT_LVDS_P   | Data out positive                                                     | 56            | 0    | V <sub>DD</sub> _DIG_IO  |       |

| STROBE_OUT_LVDS_N | Data out strobe negative                                              | 57            | 0    | V <sub>DD</sub> _DIG_IO  |       |

| STROBE_OUT_LVDS_P | Data out strobe positive                                              | 58            | 0    | V <sub>DD</sub> _DIG_IO  |       |

| RESETN            | Reset enable                                                          | 61            | I    | V <sub>DD</sub> _DIG_IO  |       |

| TEST_MODE         | Test mode                                                             | 48            | Ι    | V <sub>DD</sub> _DIG_IO  | 2     |

|                   | Clocking                                                              | 9             |      | 1                        | '     |

| хо                | Crystal output                                                        | 6             | I    | V <sub>DD</sub> _XO      |       |

| XI                | Crystal input                                                         | 7             | 0    | V <sub>DD</sub> _XO      |       |

| LVDS_160M_IO_N    | 160 MHz clock IO negative                                             | 62            | Ю    | V <sub>DD</sub> _160M_IO |       |

| LVDS_160M_IO_P    | 160 MHz clock IO positive                                             | 63            | Ю    | V <sub>DD</sub> _160M_IO |       |

|                   | I2C                                                                   |               |      |                          |       |

| I2C_CLK           | Serial clock                                                          | 60            | I    | V <sub>DD</sub> _DIG_IO  |       |

| I2C_DATA          | Serial data                                                           | 59            | Ю    | V <sub>DD</sub> _DIG_IO  |       |

|                   | Analog te                                                             | st            |      |                          |       |

| ATEST1            | Analog test 1                                                         | 4             | Ю    | V <sub>DD</sub> _XO      |       |

| ATEST2            | Analog test 2                                                         | 5             | Ю    | V <sub>DD</sub> _XO      |       |

| ATEST3            | Analog test 3                                                         | 9             | Ю    | V <sub>DD</sub> _XO      | 3     |

| ATEST4            | Analog test 4                                                         | 10            | Ю    | V <sub>DD</sub> _XO      |       |

|                   | Digital te                                                            | st            |      |                          |       |

| DTEST1            | Digital test 1                                                        | 47            | I    | V <sub>DD</sub> _DIG_IO  | 4     |

| DTEST2            | Digital test 2                                                        | 46            | I    | V <sub>DD</sub> _DIG_IO  | 4     |

|                   | Receiver Cha                                                          | nnel 1        |      |                          |       |

| RX1_LB_IN         | Low band input Receiver<br>Channel 1 received signal                  | 1             | I    | V <sub>DD</sub> _RX1     |       |

| RX1_HB_IN         | High band input Receiver<br>Channel 1 received signal                 | 3             | I    | V <sub>DD</sub> _RX1     |       |

| RXBB1_OUT_I_N     | Base band I output negative differential signal of received channel 1 | 20            | 0    | V <sub>DD</sub> _BB1     |       |

9

Table 1. Pinout list by bus (continued)

| Signal        | Signal description                                                                | Package<br>pin | Pin<br>type          | Power supply          | Notes |

|---------------|-----------------------------------------------------------------------------------|----------------|----------------------|-----------------------|-------|

|               |                                                                                   | number         | турс                 |                       |       |

| RXBB1_OUT_I_P | 19                                                                                | 0              | V <sub>DD</sub> _BB1 |                       |       |

| RXBB1_OUT_Q_N | Base band Q output negative differential signal of received channel 1             | 21             | 0                    | V <sub>DD</sub> _BB1  |       |

| RXBB1_OUT_Q_P | Base band Q output positive differential signal of received channel 1             | 22             | 0                    | V <sub>DD</sub> _BB1  |       |

|               | Receiver Cha                                                                      | nnel 2         |                      |                       |       |

| RX2_LB_IN     | Low band input Receiver<br>Channel 2 received signal                              | 39             | I                    | V <sub>DD</sub> _TRX2 |       |

| RX2_HB_IN     | High band input Receiver<br>Channel 2 received signal                             | 45             | I                    | V <sub>DD</sub> _TRX2 |       |

| RXBB2_OUT_I_N | Base band I output negative differential signal of received channel 2             | 30             | 0                    | V <sub>DD</sub> _BB2  |       |

| RXBB2_OUT_I_P | Base band I output positive differential signalof received channel 2              | 29             | 0                    | V <sub>DD</sub> _BB2  |       |

| RXBB2_OUT_Q_N | Base band Q output negative differential signal of received channel 2             | 31             | 0                    | V <sub>DD</sub> _BB2  |       |

| RXBB2_OUT_Q_P | Base band Q output positive differential signal of received channel 2             | 32             | 0                    | V <sub>DD</sub> _BB2  |       |

|               | Observation Ch                                                                    | nannel 1       |                      |                       | •     |

| RO1_LB_IN     | Low band input Observation<br>Channel 1 received signal                           | 11             | I                    | V <sub>DD</sub> _RO1  |       |

| RO1_HB_IN     | High band input Observation<br>Channel 1 received signal                          | 13             | I                    | V <sub>DD</sub> _RO1  |       |

| ROBB1_OUT_I_N | Base band I output negative differential signal of received Observation Channel 1 | 16             | 0                    | V <sub>DD</sub> _BB1  |       |

| ROBB1_OUT_I_P | Base band I output positive differential signal of received Observation Channel 1 | 15             | 0                    | V <sub>DD</sub> _BB1  |       |

| ROBB1_OUT_Q_N | Base band Q output negative differential signal of received Observation Channel 1 | 17             | 0                    | V <sub>DD</sub> _BB1  |       |

| ROBB1_OUT_Q_P | Base band Q output positive differential signal of received Observation Channel 1 | 18             | 0                    | V <sub>DD</sub> _BB1  |       |

|               | Observation Ch                                                                    | nannel 2       |                      | •                     |       |

| RO2_HB_IN     | High band input Observation<br>Channel 2 received signal                          | 37             | I                    | V <sub>DD</sub> _RO2  |       |

Table 1. Pinout list by bus (continued)

| Signal                                                               | Signal description                                                                      | Package<br>pin<br>number | Pin<br>type          | Power supply          | Notes |

|----------------------------------------------------------------------|-----------------------------------------------------------------------------------------|--------------------------|----------------------|-----------------------|-------|

| ROBB2_OUT_I_N                                                        | 34                                                                                      | 0                        | V <sub>DD</sub> _BB2 |                       |       |

| ROBB2_OUT_I_P                                                        | Base band I output positive<br>differential signal of received<br>Observation Channel 2 | 33                       | 0                    | V <sub>DD</sub> _BB2  |       |

| ROBB2_OUT_Q_N                                                        | Base band Q output negative differential signal of received Observation Channel 2       | 35                       | 0                    | V <sub>DD</sub> BB2   |       |

| ROBB2_OUT_Q_P                                                        | Base band Q output positive<br>differential signal of received<br>Observation Channel 2 | 36                       | 0                    | V <sub>DD</sub> BB2   |       |

|                                                                      | Transmit Ch                                                                             | annel                    | •                    | •                     | •     |

| TX_LB_OUT                                                            | Transmit low band output                                                                | 41                       | 0                    | V <sub>DD</sub> _TRX2 |       |

| TX_HB_OUT                                                            | Transmit high band output                                                               | 43                       | 0                    | V <sub>DD</sub> _TRX2 |       |

| TXBB_IN_Q_P                                                          | Base band Q input positive differential transmit signal                                 | 28                       | I                    | V <sub>DD</sub> _BB2  |       |

| TXBB_IN_I_P  Base band I input positive differential transmit signal |                                                                                         | 25                       | I                    | V <sub>DD</sub> _BB2  |       |

| TXBB_IN_I_N                                                          | Base band I input negative differential transmit signal                                 | 26                       | I                    | V <sub>DD</sub> _BB2  |       |

| TXBB_IN_Q_N                                                          | Base band Q input negative differential transmit signal                                 | 27                       | I                    | V <sub>DD</sub> _BB2  |       |

|                                                                      | Power                                                                                   |                          | !                    |                       |       |

| VDD_RX1                                                              | Channel 1 receiver supply                                                               | 2                        | -                    | -                     |       |

| VDD_XO                                                               | Oscillator supply                                                                       | 8                        | -                    | -                     |       |

| VDD_RO1                                                              | Observer 1 input supply                                                                 | 12                       | -                    | -                     |       |

| VDD_BB1                                                              | Base band channel 1 and observer 1 supply                                               | 14                       | -                    | -                     |       |

| VDD_SYNTH                                                            | Synthesizer supply                                                                      | 23                       | -                    | -                     |       |

| VDD_BB2                                                              | Base band channel 2 and observer 2 supply                                               | 24                       | -                    | -                     |       |

| VDD_RO2                                                              | Observer 2 input supply                                                                 | 38                       | -                    | -                     |       |

| VDD1_TRX2                                                            | Channel 2 receiver and transmitter supply                                               | 40                       | -                    | -                     |       |

| VDD2_TRX2                                                            | Channel 2 receiver and transmitter supply                                               | 42                       | -                    | -                     |       |

| VDD3_TRX2                                                            | Channel 2 receiver and transmitter supply                                               | 44                       | -                    | -                     |       |

| VDD_DIG_IO                                                           | Digital IO supply                                                                       | 53                       | -                    | -                     |       |

| VDD_DIG_CORE                                                         | Digital Core supply                                                                     | 54                       | -                    | -                     |       |

| VDD_160M_IO                                                          | Clocking IO supply                                                                      | 64                       | -                    | -                     |       |

|                                                                      | 11.7                                                                                    | 64                       | -                    | -                     |       |

Table 1. Pinout list by bus (continued)

| Signal | Signal description | Package<br>pin<br>number | Pin<br>type | Power supply | Notes |

|--------|--------------------|--------------------------|-------------|--------------|-------|

| GND    | Ground             | 65                       | -           | -            | 5     |

- 1. A 100 Ohms resistor should be placed between this pad and the other polarity pad.

- 2. In normal mode should be pulled to ground.

- 3. Application requires pull-down 10 +/-1% KOhm resistor.

- 4. This pin can be left unconnected since they are configured as inputs with internal pull-down at reset.

- 5. The 65th pin serves as a ground and thermal pad.

This section describes the DC and AC electrical specifications for the chip. This section describes the DC and AC electrical specifications of the interfaces and signals for the chip.

### 3.1 Overall DC electrical characteristics

This section describes the ratings, conditions, and other characteristics.

### 3.1.1 Absolute maximum ratings

This table provides the absolute maximum ratings.

Table 2. Absolute maximum ratings<sup>1,2</sup>

| Characteristic              | Symbol       | Min   | Max  | Unit | Notes |

|-----------------------------|--------------|-------|------|------|-------|

| Analog supply voltages      | VDD_RX1      | -0.50 | 2.00 | V    |       |

|                             | VDD_XO       | -0.50 | 2.00 | V    |       |

|                             | VDD_RO1      | -0.50 | 2.00 | V    |       |

|                             | VDD_BB1      | -0.50 | 2.00 | V    |       |

|                             | VDD_SYNTH    | -0.50 | 2.00 | V    |       |

|                             | VDD_BB2      | -0.50 | 2.00 | V    |       |

|                             | VDD_RO2      | -0.50 | 2.00 | V    |       |

|                             | VDD_TRX2     | -0.50 | 2.00 | V    |       |

|                             | VDD_160M_IO  | -0.5  | 2.00 | V    |       |

| Digital core supply voltage | VDD_DIG_CORE | -0.50 | 1.00 | V    |       |

| Digital I/O supply voltage  | VDD_DIG_IO   | -0.50 | 2.00 | V    |       |

Table continues on the next page...

RF112 Transceiver Data Sheet, Rev. 1, 06/2024

Table 2. Absolute maximum ratings<sup>1,2</sup> (continued)

| Characteristic                     | Symbol                     | Min   | Max  | Unit | Notes                                     |

|------------------------------------|----------------------------|-------|------|------|-------------------------------------------|

| Maximum voltage on non-supply pins | Digital pins, incl. GPIO:s | -0.50 | 2.00 | V    |                                           |

|                                    | Analo pins                 | -0.50 | 1.1  | V    |                                           |

| Latch-up                           | Pass                       |       | •    |      | JESD78                                    |

| Maximum RF input                   |                            |       | +5   | dBm  | Peak<br>power, all<br>frequenc<br>y bands |

| Max ESD voltage, HBM               | RF pins and BB pins        | 1000  |      | V    | ANSI-                                     |

|                                    | Other pins                 | 2000  |      | V    | JEDEC<br>JS-011-2<br>011                  |

| Max ESD voltage, CDM               | RF pins and BB pins        | 250   |      | V    | ANSI-                                     |

|                                    | Other pins                 | 500   |      | V    | JEDEC<br>JS-011-2<br>011                  |

| Storage temperature                | T <sub>STG</sub>           | -55   | 150  | ° C  |                                           |

#### Notes:

### 3.1.2 Recommended operating conditions

This table provides the recommended operating conditions for this chip.

#### NOTE

The values shown are the recommended operating conditions and proper device operation outside these conditions is not guaranteed.

Table 3. Recommended operating conditions

| Characteristic | Symbol    | Min  | Тур  | Max  | Unit | Notes |

|----------------|-----------|------|------|------|------|-------|

| Analog supply  | VDD_RX1   | 1.62 | 1.67 | 1.72 | V    |       |

| voltage        | VDD_XO    | 1.62 | 1.67 | 1.72 | V    |       |

|                | VDD_RO1   | 1.62 | 1.67 | 1.72 | V    |       |

|                | VDD_BB1   | 1.62 | 1.67 | 1.72 | V    |       |

|                | VDD_SYNTH | 1.62 | 1.67 | 1.72 | V    |       |

|                | VDD_BB2   | 1.62 | 1.67 | 1.72 | V    |       |

Table continues on the next page...

RF112 Transceiver Data Sheet, Rev. 1, 06/2024

<sup>1.</sup> Functional operating conditions are given in this table are stress ratings only, and functional operation at the maximums is not guaranteed. Stresses beyond those listed may affect device reliability or cause permanent damage to the device.

<sup>2.</sup> Exposing device to Absolute Maximum Ratings conditions for long periods of time may affect reliability or cause permanent damage.

Table 3. Recommended operating conditions (continued)

| Characteristic                          | Symbol                                  | Min       | Тур   | Max  | Unit            | Notes                                                                   |

|-----------------------------------------|-----------------------------------------|-----------|-------|------|-----------------|-------------------------------------------------------------------------|

|                                         | VDD_RO2                                 | 1.62      | 1.67  | 1.72 | V               |                                                                         |

|                                         | VDD_TRX2                                | 1.62      | 1.67  | 1.72 | V               |                                                                         |

|                                         | VDD_160M_IO                             | 1.62      | 1.67  | 1.72 | V               |                                                                         |

| Digital supply                          | VDD_DIG_CORE                            | 0.87      | 0.90  | 0.97 | V               |                                                                         |

| voltage                                 | VDD_DIG_IO                              | 1.71      | 1.80  | 1.89 | V               |                                                                         |

| Low frequency                           | 1 kHz ≤ fRipple ≤ 50 MHz                | Z         |       | 1    |                 | 1                                                                       |

| Analog supply ripple                    | Single tone                             |           |       | 10   | mVp             |                                                                         |

| прріе                                   | Total ripple                            |           |       | 14   | mVrms           |                                                                         |

| High frequency                          | 4.9 GHz ≤ fRipple ≤ 6.2 (               | GHz       | 1     | 1    |                 | -                                                                       |

| Analog supply ripple                    | Single tone                             |           |       | 2.5  | mVpp            |                                                                         |

| Analog supply                           | 1 kHz ≤ fNoise ≤ 30 kHz                 |           | 1000  | 2000 | nV/ √ Hz        |                                                                         |

| noise                                   | fNoise = 100 kHz                        |           | 200   | 400  | nV/ √ Hz        |                                                                         |

|                                         | fNoise = 1.0 MHz                        |           | 20    | 40   | nV/ √ Hz        |                                                                         |

|                                         | fNoise = 10 MHz                         |           |       | 4    | nV/ √ Hz        |                                                                         |

|                                         | fNoise > 50 MHz                         |           |       | 1    | nV/ <b>√</b> Hz |                                                                         |

|                                         | 4.9 GHz ≤ fNoise ≤ 6.2<br>GHz           |           |       | 1    | nV/ <b>√</b> Hz |                                                                         |

| Operating temperature                   | TA, ambient temperature                 | 0         |       |      | ° C             |                                                                         |

| range                                   | TJ, junction temperature                |           |       | 105  | ° C             |                                                                         |

| Extended<br>Operating                   | TA, ambient temperature                 | -40       |       |      | ° C             |                                                                         |

| temperature range                       | TJ, junction temperature                |           |       | 105  | ° C             |                                                                         |

| Reference clock frequency               | Crystal or external clock source        | 40        | MHz   |      |                 |                                                                         |

| Crystal load capacitance                | Effective differential load capacitance | 5         | 10    | 12   | pF              | Implemented<br>on-chip as<br>single-ended<br>capacitors on XI<br>and XO |

| External Clock<br>Source Input<br>Level | XO CMOS input                           | 0.80      |       | 0.99 | Vpp             |                                                                         |

| External Clock<br>Source Duty<br>Cycle  | XO CMOS input                           | 45        | 50    | 55   | %               |                                                                         |

| External Clock                          | TCXO CMOS input at 40                   | MHz frequ | iency | •    | ·               |                                                                         |

| Source Phase<br>Noise                   | Offset = 10 kHz                         |           |       | -143 | dBc/Hz          |                                                                         |

| 140190                                  | Offset = 100 kHz                        |           |       | -155 |                 |                                                                         |

|                                         | Offset = 1 MHz and above                |           |       | -160 |                 |                                                                         |

Table 3. Recommended operating conditions (continued)

| Characteristic                                                 | Symbol                     | Min  | Тур | Max  | Unit | Notes |

|----------------------------------------------------------------|----------------------------|------|-----|------|------|-------|

| Input external<br>clock differential<br>input voltage<br>level | LVDS_160M_IO_P/N<br>Input  | 200  | 400 |      | mVpp | 1     |

| Input external clock input common mode voltage level           | LVDS_160M_IO_P/N<br>Input  | 0.2  |     | 1.2  | V    | 1     |

| Input external clock duty cycle                                | LVDS_160M_IO_P/N<br>Input  | 45   | 50  | 55   | %    | 1     |

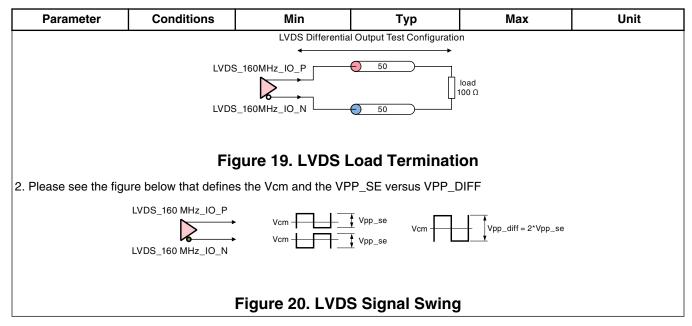

| Output<br>reference clock<br>output load                       | LVDS_160M_IO_P/N<br>output |      | 100 |      | Ω    | 1     |

| Rx BB external                                                 | R1                         |      | 50  |      | Ω    | 3     |

| output load (kick -back filter)                                | C1                         |      | 10  |      | pF   | 3     |

| TX BB input common mode                                        |                            |      |     | 0.5  | V    |       |

| TX BB input signal level                                       | Full scale from DAC        |      |     | 0.35 | Vp   |       |

| Frequency                                                      | HB Lowest                  |      |     | 4900 | MHz  |       |

| Range                                                          | HB Highest                 | 6000 |     |      | MHz  |       |

|                                                                | LB Lowest                  |      |     | 2400 | MHz  |       |

|                                                                | LB Highest                 | 2500 |     |      | MHz  |       |

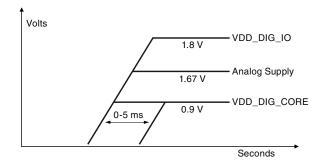

### 3.1.3 Power Sequencing

Power rails can ramp simultaneously for all voltages, Core power supplies VDD\_DIG\_CORE (0.9V) should not begin to ramp before other supplies, and should reach 90% of nominal voltage no more than 5ms after I/O rails ramp as shown in the figure below. Analog 1.67 V supply and I/O 1.8 V supply are expected to begin ramp simultaneously.

Figure 5. RF112 Transceiver power sequencing

### General specification

#### **Receiver specification** 3.3

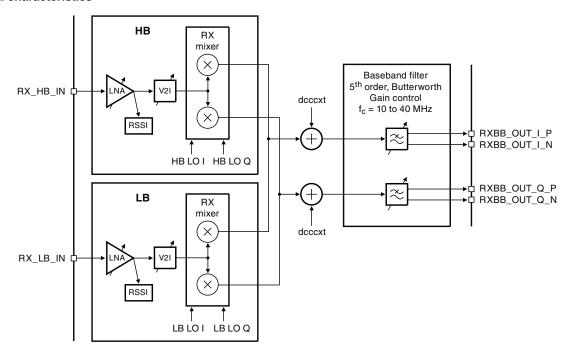

Each TRX receiver consist of two identical dual band chains with shared baseband filters, as shown in the figure below. The main building blocks consist of the LNA, the mixer and the active leapfrog lowpass filter. The double-sided bandwidth of the analog filter supports a large range of fixed settings ranging from 20 to 80 MHz. The filter bandwidth needs to be calibrated by the baseband chip. The analog receiver gain can be controlled at RF and in the active analog filter. The peak envelop signal can be measured at RF before baseband filtering.

The figure below shows the detailed block diagram of one receive chain. The second receive chain and the observation chains are identical, except for the RO2 chain which has no LB input.

RF112 Transceiver Data Sheet, Rev. 1, 06/2024

Figure 6. Block diagram of one receive chain.

The receive data path is DC coupled to avoid settling issues. To mitigate offset errors it is recommended to perform offset compensation at the input of the active analog filter. The DC offset compensation algorithm has to be run in the baseband.

The observation receivers are identical to the TRX receivers, except for that the second observation receiver has no LB chain.

### 3.3.1 RxRF RSSI

The RxRF RSSI have three detection levels, that needs to be sampled at a nominal rate of 20 MSps using sample clocks derived from the 160 MHz synthesizer, synchronized for all four receiver branches.

The decay rate of the peak detectors can be configurable to allow for a setting with nonsignificant decay during a 50 ns sampling interval, but not so slow decay that it becomes unable to track a change in signal level due to a radar pulse falling edge, that is caused by out-of-band RADAR pulses which change the energy level for short durations of 500-1000 ns in a periodic pattern.

The sampling in the analog detector is done using the 160 MHz clock from the synthesizer, down-sampling and filtering is performed in the digital core.

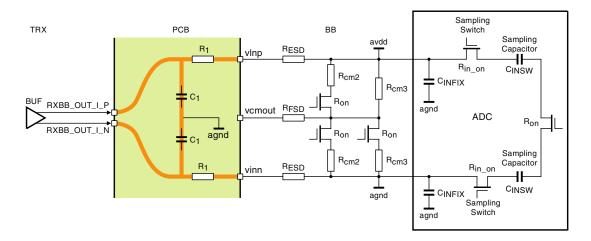

### 3.3.2 Rx BB interface

The Rx BB output shall be connected to the ADC input in the baseband chip as shown in below:

Figure 7. Connection of Rx BB output of transceiver chip (TRX) to ADC input of baseband chip (BB). Note that Rcm2 and Rcm3 shall be disconnected, input common mode voltage of the ADC is set by the Rx BB output buffer.

This table shows receiver specification. All RF signal levels are referred to the input of an ideal matching network with no losses.

**Conditions** Unit **Parameter** Min Typ Max RX input HB and LB, 50 Ω impedance differential, including matching RX input return HB and LB, all gain 6 >10 dB loss, IS11I settings, including matching Maximum gain setting All channel bandwidths RMS value over all subcarrier freq Noise figure 4900 MHz 4.5 dB 5300 MHz 4.9 dB 6000 MHz 5.4 dΒ 4.4 dΒ 2400-2500 MHz -10 -20 dBm Max input signal Minimum gain level RMS power of OFDM burst where

Table 4. Receiver specification

Table continues on the next page...

correction and demodulation (data-aided equalization enabled).

Over process, voltage and temp (PVT):

RMS value over all subcarriers. All values are applicable at both -40 dBm and -23 dBm. Ideal IQ

EVM ≤ -32 dB

RX1, RX2, RO1,

and RO2 EVM

Table 4. Receiver specification (continued)

| Parameter                | Conditions                                | Min                  | Тур | Max | Unit |

|--------------------------|-------------------------------------------|----------------------|-----|-----|------|

|                          | 4900 MHz, ChBW:                           |                      | -40 | -36 | dB   |

|                          | 20/40 MHz, PVT                            |                      |     |     |      |

|                          | 4900 MHz, ChBW:<br>80 MHz, PVT            |                      | -39 | -36 | dB   |

|                          | 5300 MHz, ChBW:<br>20/40 MHz, PVT         |                      | -39 | -36 | dB   |

|                          | 5300 MHz, ChBW:<br>80 MHz, PVT            |                      | -38 | -36 | dB   |

|                          | 6000 MHz, ChBW:<br>20/40 MHz, PVT         |                      | -38 | -36 | dB   |

|                          | 6000 MHz, ChBW:<br>80 MHz, PVT            |                      | -37 | -36 | dB   |

|                          | 2400-2500 MHz,<br>ChBW: 20/40 MHz,<br>PVT |                      | -39 | -36 | dB   |

|                          | Room temperature (                        | RT), TJ ≈ 50 ° C     |     | ·   | •    |

|                          | 4900 MHz, ChBW:<br>20/40 MHz, PV          |                      |     | -38 | dB   |

|                          | 4900 MHz, ChBW:<br>80 MHz, PV             |                      |     | -37 | dB   |

|                          | 5300 MHz, ChBW:<br>20/40 MHz, PV          |                      |     | -38 | dB   |

|                          | 5300 MHz, ChBW:<br>80 MHz, PV             |                      |     | -37 | dB   |

|                          | 6000 MHz, ChBW:<br>20/40 MHz, PV          |                      |     | -38 | dB   |

|                          | 6000 MHz, ChBW:<br>80 MHz, PV             |                      |     | -36 | dB   |

| Gain specification       |                                           |                      | -   |     |      |

| RX total gain            | Gain into 100 Ω load                      | i.                   |     |     |      |

|                          | Minimum, HB                               |                      |     | 5.5 | dB   |

|                          | Maximum, HB                               | 61.5                 |     |     | dB   |

|                          | Minimum, LB                               |                      |     | 2   | dB   |

|                          | Maximum, LB                               | 65                   |     |     | dB   |

| RX gain variation        | Over temperature. F                       | or all gain settings | ;   |     | •    |

|                          | НВ                                        | -4                   |     | +4  | dB   |

|                          | LB                                        | -4                   |     | +4  | dB   |

| RX RF gain control       | НВ                                        |                      | 38  |     | dB   |

| range                    | LB                                        |                      | 41  |     | dB   |

| RX RF gain               | Max-Min; over frequ                       | ency.                |     |     | •    |

| flatness                 | НВ                                        |                      |     | 2.5 | dB   |

|                          | LB                                        |                      |     | 1   | dB   |

| RX BB gain control range |                                           |                      | 30  |     | dB   |

Table 4. Receiver specification (continued)

|                                                                          | Conditions                                                                                                                                              | Min            | Тур                   | Max   | Unit                    |

|--------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|-----------------------|-------|-------------------------|

| RX gain step                                                             | RF HB                                                                                                                                                   |                | 5.5                   |       | dB                      |

|                                                                          | RF LB                                                                                                                                                   |                | 6                     |       | dB                      |

|                                                                          | Analog baseband                                                                                                                                         |                | 3                     |       | dB                      |

| RX gain settling time                                                    | Gain settled to ± 1<br>dB of steady state<br>after gain update<br>command (20MHz<br>channel BW)                                                         |                |                       | 200   | ns                      |

|                                                                          | Excluding LLCP transfer time.                                                                                                                           |                |                       |       |                         |

| Analog filter                                                            |                                                                                                                                                         | 1              |                       | -     | -                       |

| Analog RX filter                                                         | 5th order Butterwort                                                                                                                                    | n, 3 dB point  |                       |       |                         |

| cutoff frequency                                                         | Ch BW 20 MHz                                                                                                                                            |                | 12.5                  |       | MHz                     |

| (signal bandwidth is                                                     | Ch BW 40 MHz                                                                                                                                            |                | 25.0                  |       | MHz                     |

| twice the cutoff)                                                        | Ch BW 80 MHz                                                                                                                                            |                | 50.0                  |       | MHz                     |

| Accuracy of analog<br>RX filter cutoff<br>frequency after<br>calibration |                                                                                                                                                         | -7             |                       | +7    | %                       |

| Analog RX filter suppression                                             | At center of adjacent channel                                                                                                                           |                | 18                    |       | dB                      |

|                                                                          | At center of alternate channel                                                                                                                          |                | 48                    |       | dB                      |

| Analog RX filter<br>group delay<br>variation                             | given values are the                                                                                                                                    |                | up delay at DC, norma |       | nnel bandwidth, i.e. th |

|                                                                          | $fchBW = \{20, 40, 80\}$                                                                                                                                | MHz            |                       | ,     |                         |

|                                                                          | fchBW = {20, 40, 80}<br>Range: 0 to 30% of fchBW                                                                                                        |                |                       | +0.35 |                         |

|                                                                          | Range: 0 to 30% of                                                                                                                                      |                |                       |       |                         |

| Analog RX signal path delay                                              | Range: 0 to 30% of fchBW Range: 30% to                                                                                                                  | -0.35          | 1/B                   | +0.35 | S                       |

| path delay                                                               | Range: 0 to 30% of fchBW  Range: 30% to 46% of fchBW  Channel bandwidth B = 20/40/80 MHz                                                                | -0.35          | 1/B                   | +0.35 | s                       |

| path delay  Analog RX                                                    | Range: 0 to 30% of fchBW  Range: 30% to 46% of fchBW  Channel bandwidth B = 20/40/80 MHz  Cannot be                                                     | -0.35          | 1/B                   | +0.35 |                         |

| path delay                                                               | Range: 0 to 30% of fchBW Range: 30% to 46% of fchBW Channel bandwidth B = 20/40/80 MHz Cannot be measured                                               | -0.35          | 1/B                   | +0.35 | s V                     |

| Analog RX baseband output                                                | Range: 0 to 30% of fchBW Range: 30% to 46% of fchBW Channel bandwidth $B = 20/40/80 \text{ MHz}$ Cannot be measured Into 100 $\Omega$ load. Common mode | -0.35<br>-0.80 | 1/B                   | +0.35 |                         |

Table 4. Receiver specification (continued)

| Parameter                                        | Conditions                                                                               | Min                  | Тур    | Max | Unit |

|--------------------------------------------------|------------------------------------------------------------------------------------------|----------------------|--------|-----|------|

| Resolution of RX<br>DC offset comp. at<br>output | Maximum<br>baseband gain                                                                 |                      | ± 5    |     | mV   |

| DC offset at output after calibration            | Maximum gain Measurement                                                                 | -50                  |        | 50  | mV   |

|                                                  | bandwidth ≤ 10 kHz                                                                       |                      |        |     |      |

| Rx image rejection ratio                         | Uncalibrated                                                                             | 25                   |        |     | dB   |

| RSSI                                             |                                                                                          |                      |        |     |      |

| RSSI thresholds                                  | referred to the 1dB of                                                                   | compression point (C | P1dB)  |     |      |

|                                                  | High threshold                                                                           |                      | -6     |     | dBc  |

|                                                  | Middle threshold                                                                         |                      | -15    |     | dBc  |

|                                                  | Low threshold                                                                            |                      | -24    |     | dBc  |

| RSSI accuracy                                    |                                                                                          |                      | +/-3.2 |     | dB   |

| RSSI sample rate                                 | Configurable                                                                             | 10/20                |        |     | MSps |

| General                                          |                                                                                          |                      |        |     |      |

| EVM degradation<br>due to Rx spurious<br>signal  | Degradation compared to neighboring channel.                                             |                      |        | 3   | dB   |

|                                                  | RF level chosen to<br>give -30dB EVM<br>with maximum gain<br>for neighboring<br>channel. |                      |        |     |      |

|                                                  | 40 MHz channel bandwidth.                                                                |                      |        |     |      |

| Rx RF pin isolation                              | See Table 6                                                                              |                      |        |     |      |

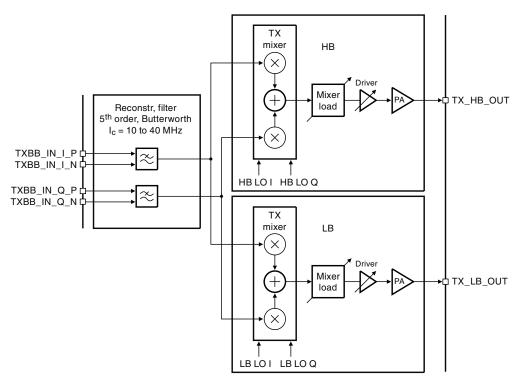

### 3.4 Transmitter specification

The transmitter consists of a high band and a low band RF chain with shared baseband reconstruction filter, see figure below.

A fifth order Butterworth reconstruction filter suppresses the DAC alias signals, the filter bandwidth needs to be calibrated by the baseband chip. The baseband signal is then upconverted and amplified. The LO leakage depends on the DC offset and needs to be minimized by DC offset compensation of the digital signal in the baseband. The TX gain can be adjusted at several places and most of the gain control is done at RF to ensure that the LO leakage remains low for all output power levels.

Figure 8. Detailed block diagram of the transmit chains

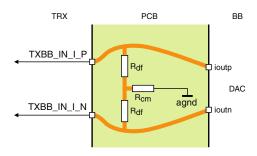

### 3.4.1 Tx BB interface

The Tx BB input shall be connected to the DAC output in the baseband chip as shown in figure below:

Figure 9. Tx BB interface

The DAC settings and external resistors Rdif and Rcm must be chosen to fulfill the TX BB input common mode and input signal level requirements.

RF112 Transceiver Data Sheet, Rev. 1, 06/2024

This table shows the transmitter specification. Unless otherwise specified, all values assume that the receivers are disabled. All RF signal levels are referred to the output of an ideal matching network with no losses.

Table 5. Transmitter specification

| Parameter                   | Conditions                                                            | Min                                | Тур                   | Max                  | Unit |  |  |  |

|-----------------------------|-----------------------------------------------------------------------|------------------------------------|-----------------------|----------------------|------|--|--|--|

| RF channel<br>bandwidth     | ChBW                                                                  | 20/40/80                           |                       |                      | MHz  |  |  |  |

| Signal modulation standards | 802.11b/g/a/n/ax                                                      |                                    |                       |                      |      |  |  |  |

| TX output return<br>loss    | 50 Ω characteristics impedance, Including off-chip impedance matching | 6                                  |                       |                      | dB   |  |  |  |

|                             | -6 dBm output level                                                   |                                    |                       |                      |      |  |  |  |

| TX EVM                      | RMS value over all s                                                  | subcarriers. All values            | are applicable at bot | th -6 dBm and -26 dE | Bm.  |  |  |  |

|                             | Ideal IQ correction a                                                 | nd demodulation (data              | a-aided equalization  | enabled).            |      |  |  |  |

|                             | Over process, voltag                                                  | ge and temp (PVT):                 |                       |                      |      |  |  |  |

|                             | 4900 MHz, ChBW:<br>20/40 MHz, PVT                                     |                                    | -41                   | -36                  | dB   |  |  |  |

|                             | 4900 MHz, ChBW:<br>80 MHz, PVT                                        |                                    | -39                   | -36                  | dB   |  |  |  |

|                             | 5300 MHz, ChBW:<br>20/40 MHz, PVT                                     |                                    | -40                   | -36                  | dB   |  |  |  |

|                             | 5300 MHz, ChBW:<br>80 MHz, PVT                                        |                                    | -38                   | -36                  | dB   |  |  |  |

|                             | 6000 MHz, ChBW:<br>20/40 MHz, PVT                                     |                                    | -39                   | -36                  | dB   |  |  |  |

|                             | 6000 MHz, ChBW:<br>80 MHz, PVT                                        |                                    | -37                   | -36                  | dB   |  |  |  |

|                             | 2400-2500 MHz,<br>ChBW: 20/40 MHz,<br>PVT                             |                                    | -44                   | -38                  | dB   |  |  |  |

|                             | Room temperature (                                                    | Room temperature (RT), TJ ≈ 50 ° C |                       |                      |      |  |  |  |

|                             | 4900 MHz, ChBW:<br>20/40 MHz, PV                                      |                                    |                       | -38                  | dB   |  |  |  |

|                             | 4900 MHz, ChBW:<br>80 MHz, PV                                         |                                    |                       | -38                  | dB   |  |  |  |

|                             | 5300 MHz, ChBW:<br>20/40 MHz, PV                                      |                                    |                       | -38                  | dB   |  |  |  |

|                             | 5300 MHz, ChBW:<br>80 MHz, PV                                         |                                    |                       | -38                  | dB   |  |  |  |

|                             | 6000 MHz, ChBW:<br>20/40 MHz, PV                                      |                                    |                       | -38                  | dB   |  |  |  |

|                             | 6000 MHz, ChBW:<br>80 MHz, PV                                         |                                    |                       | -37                  | dB   |  |  |  |

Table 5. Transmitter specification (continued)

| Parameter                                                      | Conditions                                                                                                                     | Min                                             | Тур                 | Max                      | Unit                |

|----------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------|---------------------|--------------------------|---------------------|

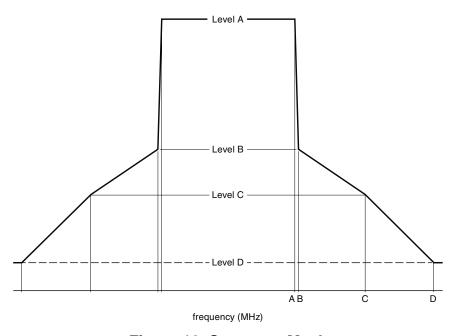

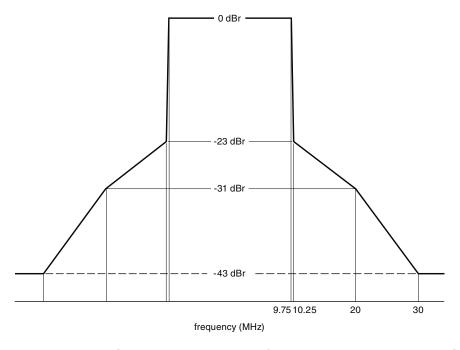

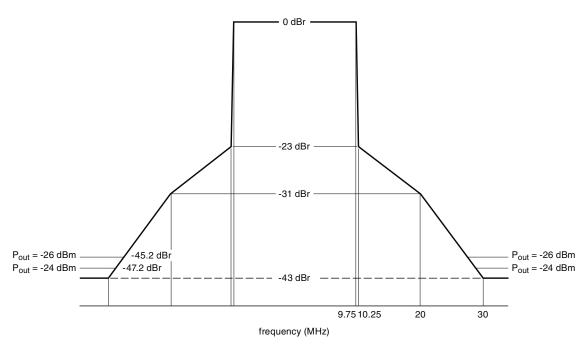

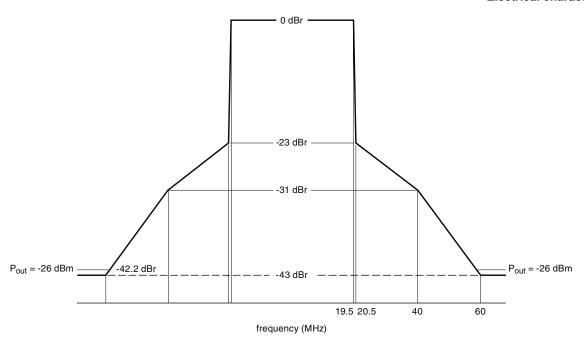

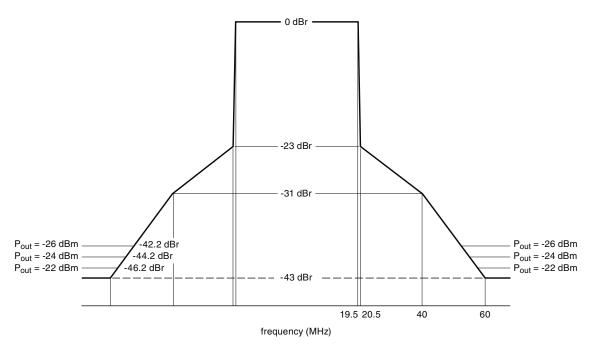

| TX spectrum mask                                               |                                                                                                                                | er than standard, exce<br>15, also see spectrum |                     | ΓX noise floor, in the t | igure examples from |

|                                                                | ChBW 20MHz: [A =                                                                                                               | 9.75MHz, B = 10.25M                             | MHz, C = 20MHz, D : | = 30MHz ]                |                     |

|                                                                | level B                                                                                                                        | ,                                               | , ,                 | -23                      | dBr                 |

|                                                                | level C                                                                                                                        |                                                 |                     | -31                      | dBr                 |

|                                                                | level D, HB                                                                                                                    |                                                 |                     | -43                      | dBr                 |

|                                                                | level D, LB                                                                                                                    |                                                 |                     | -48                      | dBr                 |

|                                                                | ChBW 40MHz: [A =                                                                                                               | 19.5MHz, B = 20.5Mł                             | Hz, C = 40MHz, D =  | <br>60MHz]               |                     |

|                                                                | level B                                                                                                                        |                                                 |                     | -23                      | dBr                 |

|                                                                | level C                                                                                                                        |                                                 |                     | -31                      | dBr                 |

|                                                                | level D, HB                                                                                                                    |                                                 |                     | -43                      | dBr                 |

|                                                                | level D, LB                                                                                                                    |                                                 |                     | -48                      | dBr                 |

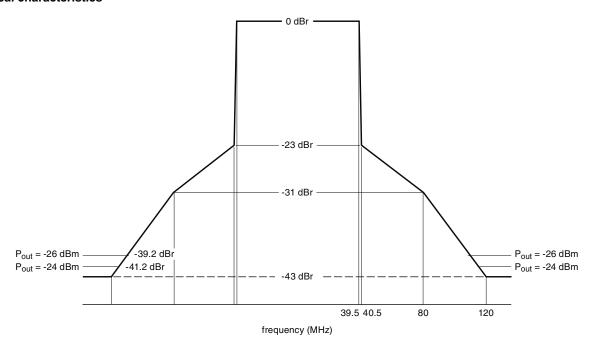

|                                                                | ChBW 80MHz (HB                                                                                                                 | only):[ A = 39.5MHz, E                          | B = 40.5MHz, C = 80 | MHz, D = 120MHz]         |                     |

|                                                                | level B                                                                                                                        |                                                 |                     | -23                      | dBr                 |

|                                                                | level C                                                                                                                        |                                                 |                     | -31                      | dBr                 |

|                                                                | level D, HB                                                                                                                    |                                                 |                     | -43                      | dBr                 |

|                                                                | level D, LB                                                                                                                    |                                                 |                     | -48                      | dBr                 |

| Transmit signal level into 50 Ohms                             | Maximum with full performance                                                                                                  | -6                                              |                     |                          | dBm                 |

| load                                                           | Minimum with full performance                                                                                                  |                                                 |                     | -26                      | dBm                 |

|                                                                | Minimum with<br>EVM<-36dB<br>(Return loss, gain<br>step etc. may be<br>out of spec, also<br>note spectrum<br>mask degradation) |                                                 | -40                 | -38                      | dBm                 |

| Power control resolution                                       |                                                                                                                                |                                                 | 2                   |                          | dB                  |

| TX gain settling time                                          | Gain settled to within ± 1 dB of steady state after gain update command                                                        |                                                 |                     | 400                      | ns                  |

| Analog filter                                                  |                                                                                                                                |                                                 | 1                   |                          |                     |

| Reconstr. filter                                               | 5th order Butterwort                                                                                                           | h, 3 dB point                                   |                     |                          |                     |

| cutoff frequency                                               | Ch BW 20 MHz                                                                                                                   |                                                 | 12.5                |                          | MHz                 |

|                                                                | Ch BW 40 MHz                                                                                                                   |                                                 | 25.0                |                          | MHz                 |

|                                                                | Ch BW 80 MHz                                                                                                                   |                                                 | 50.0                |                          | MHz                 |

| Accuracy of reconstr filter cutoff frequency after calibration |                                                                                                                                | -5                                              |                     | +5                       | %                   |

Table 5. Transmitter specification (continued)

| Parameter                    | Conditions                                      | Min                                                                                                       | Тур                   | Max                   | Unit         |  |  |  |  |

|------------------------------|-------------------------------------------------|-----------------------------------------------------------------------------------------------------------|-----------------------|-----------------------|--------------|--|--|--|--|

| Reconstr. filter suppression | At center of adjacent channel                   |                                                                                                           | 20                    |                       | dB           |  |  |  |  |

|                              | At center of alternate channel                  |                                                                                                           | 50                    |                       | dB           |  |  |  |  |

| Reconstr. filter             | Deviation of group d                            | elay from the group d                                                                                     | elay at DC, normalize | ed to half the channe | l bandwidth, |  |  |  |  |

| group delay variation        | i.e. the given values                           | are the products of $\Delta$                                                                              | gd and the nominal    | channel BW, fchBW     |              |  |  |  |  |

| variation                    | fchBW = {20, 40, 80                             | } MHz                                                                                                     |                       |                       |              |  |  |  |  |

|                              | Range: 0 to 30% of fchBW                        | -0.35                                                                                                     |                       | +0.35                 | -            |  |  |  |  |

|                              | Range: 30% to 46% of fchBW                      | -0.80                                                                                                     |                       | +0.80                 | -            |  |  |  |  |

| Analog TX signal path delay  | Channel bandwidth<br>B = 20/40/80 MHz           |                                                                                                           | 1/B                   |                       | s            |  |  |  |  |

|                              | Cannot be measured.                             |                                                                                                           |                       |                       |              |  |  |  |  |

| General                      |                                                 |                                                                                                           |                       |                       |              |  |  |  |  |

| Unwanted emissions           | 30 MHz ≤ f < 1.0<br>GHz                         |                                                                                                           |                       | -70                   | dBm          |  |  |  |  |

| below 1 GHz                  | RBW = 100 kHz                                   |                                                                                                           |                       |                       |              |  |  |  |  |

|                              | OFDM signal, P <sub>RMS_TX_burst</sub> = -6 dBm |                                                                                                           |                       |                       |              |  |  |  |  |

|                              | 40 MHz channel<br>BW                            |                                                                                                           |                       |                       |              |  |  |  |  |

| Unwanted                     | RBW = 1 MHz                                     |                                                                                                           | 1                     | 1                     |              |  |  |  |  |

| emissions                    | OFDM signal, P <sub>RMS</sub>                   | _TX_burst = -6 dBm                                                                                        |                       |                       |              |  |  |  |  |

| above 1 GHz                  | 40 MHz channel BW                               | 1                                                                                                         |                       |                       |              |  |  |  |  |

|                              | Harmonics excluded                              | I                                                                                                         |                       |                       |              |  |  |  |  |

|                              | Reference spurs exc                             | cluded                                                                                                    |                       |                       |              |  |  |  |  |

|                              | Valid for frequencies largest.                  | Valid for frequencies at least 100 MHz from the LO or outside the adjacent channel, whichever is largest. |                       |                       |              |  |  |  |  |

|                              | 1.000 GHz ≤ f <<br>3.000 GHz                    |                                                                                                           |                       | -70                   | dBm          |  |  |  |  |

|                              | 3.000 GHz ≤ f <<br>4.200 GHz                    |                                                                                                           |                       | -80                   | dBm          |  |  |  |  |

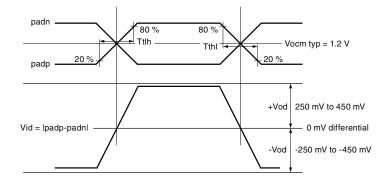

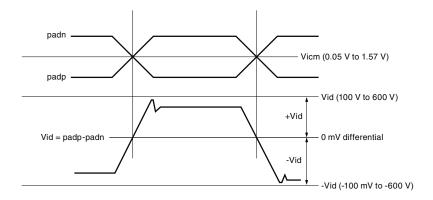

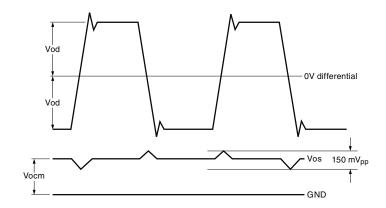

|                              | 4.200 GHz ≤ f <<br>4.500 GHz                    |                                                                                                           |                       | -80                   | dBm          |  |  |  |  |