# AN14388 TJA1445, TJA1465 application note Rev. 1.0 — 18 November 2024

**Application note**

#### **Document information**

| Information | Content                                                                                                                                                                                                                                                                             |

|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Keywords    | TJA1445, TJA1465, CAN transceiver, CAN FD, GPIO, TX enable, CAN XL passive, CAN SIC, partial networking, selective wake-up                                                                                                                                                          |

| Abstract    | This application note covers hardware and software application aspects of the TJA1445 and TJA1465 CAN transceivers for automotive applications. It assumes that the reader is familiar with the TJA1445 and TJA1465 data sheets, which describe the functionality of these devices. |

# 1 Introduction

The TJA1445<sup>[1]</sup> and TJA1465<sup>[2]</sup> are high-speed CAN transceiver ICs that provide an interface between a controller area network (CAN) or CAN FD (flexible data rate) protocol controller and the physical two-wire CAN bus. These products implement the CAN physical layer as defined in ISO 11898-2:2024 and SAE J2284-1 to SAE J2284-5, making them fully interoperable with high-speed classical CAN and CAN FD transceivers.

Both devices support CAN partial networking (PN) by means of selective wake-up functionality, making them the ideal choice for CAN system implementations where only nodes that are needed can be activated at any time. Nodes that are not needed for the function being performed can be powered down to minimize system power consumption, even when CAN bus traffic is running.

<u>Table 1</u> provides an overview of the device variants supported by this application note. All variants include an SPI for configuration, mode control and diagnostics. The 'B' variants (TJA1445B and TJA1465B) feature three general-purpose I/O pins (GPIO) and a CAN transmitter enable/disable input TXEN\_N.

Table 1. Transceiver variants

| Feature                                  | TJA1445A     | TJA1445B     | TJA1465A     | TJA1465B     |

|------------------------------------------|--------------|--------------|--------------|--------------|

| CAN transceiver type                     | HS-CAN       | HS-CAN       | CAN SIC      | CAN SIC      |

| Selective wake-up for partial networking | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ |

| Option 'CAN FD passive'                  | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ |

| Option 'CAN XL passive'                  |              |              | $\checkmark$ | $\checkmark$ |

| TJA1145A footprint and pinning           | $\checkmark$ |              | $\checkmark$ |              |

| Transmitter enable input pin             |              | $\checkmark$ |              | $\checkmark$ |

| 3 x GPIO                                 |              | $\checkmark$ |              | $\checkmark$ |

The TJA1445/65 can be configured to ignore CAN FD frames while waiting for a valid wake-up frame. This additional feature of partial networking, called CAN FD passive, is the perfect fit for networks that support a mix of classical CAN and CAN FD communications. The TJA1465 features an additional option that allows CAN XL frames to be ignored, even when they are transmitted in FAST mode. This 'CAN XL passive' feature supports a mix of all three, classical CAN, CAN FD and CAN XL communications.

The TJA1465 features CAN signal improvement capability (SIC), as defined in ISO 11898-2:2024. CAN signal improvement significantly reduces signal ringing on a network, allowing for reliable 2 Mbit/s and 5 Mbit/s CAN FD communication in larger and more complex topologies. Tight bit timing symmetry enables CAN FD communication up to 8 Mbit/s.

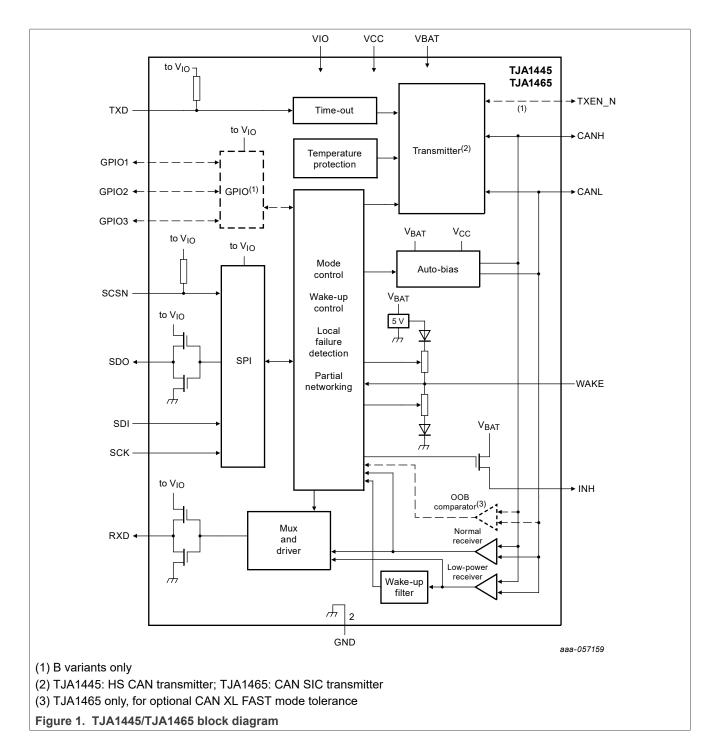

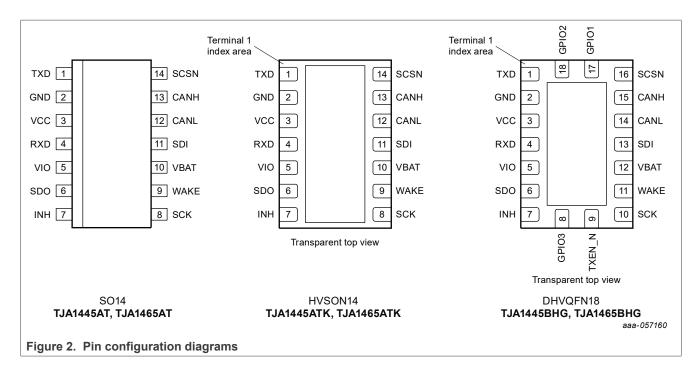

The TJA1445 and TJA1465 share the same block diagram (Figure 1) and pinning (Figure 2).

# **NXP Semiconductors**

# AN14388

### TJA1445, TJA1465 application note

# **NXP Semiconductors**

# AN14388

TJA1445, TJA1465 application note

# 2 Hardware design

In this section, typical hardware applications using the transceiver are discussed. For functional safety aspects, see the related safety manual <sup>[4]</sup>.

# 2.1 Power supply

### 2.1.1 Power supply configuration

# 2.1.1.1 Supply pins VBAT, VCC and VIO

A TJA1445/65 device needs power supply connections on three pins:

- Pin VCC must be connected to a regulated 5 V supply (V<sub>CC</sub>). Optionally, V<sub>CC</sub> can be turned off while the device is in a low-power mode (Standby, Sleep or low-power ListenOnly mode).

- Pin VBAT can be connected to the rectified and filtered 12 V car battery ( $V_{BAT}$ ), or to  $V_{CC}$  (5 V). It is the main power supply pin for the device and must be supplied in all operating modes. When  $V_{CC}$  is expected to be turned off in a low-power mode,  $V_{BAT}$  must be higher than 5.5 V for proper CAN bias generation.

- Pin VIO should be connected to the same regulated 1.8 V, 3.3 V or 5 V V<sub>IO</sub> supply rail supplying the port pins of the connected microcontroller (MCU). Optionally, V<sub>IO</sub> can be turned off when the device is in Sleep mode.

The power supply rails can be ramped up or down in arbitrary order. However, to ensure the device powers up without automatically transitioning to Sleep mode,  $V_{IO}$  must have ramped up within  $t_{det(uv)long2}$  after  $V_{BAT}$  has exceeded its undervoltage detection threshold,  $V_{uvd(VBAT)}$ .

### 2.1.1.2 INH output pin

The INH output may be used for automatic  $V_{CC}$  and/or  $V_{IO}$  voltage regulator control:

- either for direct on/off control of regulators via the corresponding input pins (see also Section 2.1.4) or

- as a wake-up signal for system basis chips or power management ICs (see also Section 2.4.1).

However, when pins VBAT and VCC are both supplied from  $V_{CC}$ ,  $V_{CC}$  must be available while the device is in Sleep mode. Otherwise, the wake-up functionality of the device would be lost.

When INH controls the microcontroller supply, the microcontroller should start up at the same, or lower,  $V_{BAT}$  level as the TJA1445/65 device. Otherwise, when  $V_{BAT}$  ramps up slowly, the microcontroller may not be able to start SPI communication with the device before the MCU time-out time  $t_{to(MCU)}$  has elapsed, and the device would automatically enter Sleep mode.

When the  $V_{BAT}$  supply level sits at, or around, the undervoltage detection threshold  $V_{uvd(VBAT)}$  for some time, the INH signal may switch frequently on and off. The application must tolerate this behavior.

When INH is not used, it can be left unconnected or connected to pin VBAT.

### 2.1.1.3 Power supply configuration examples

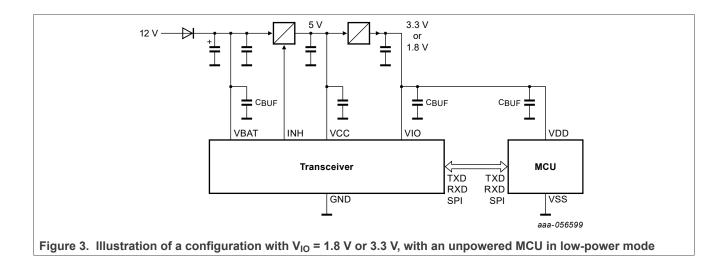

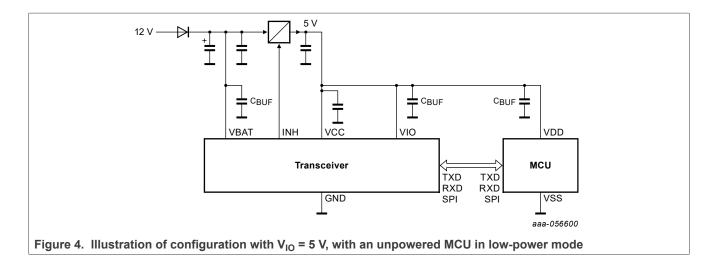

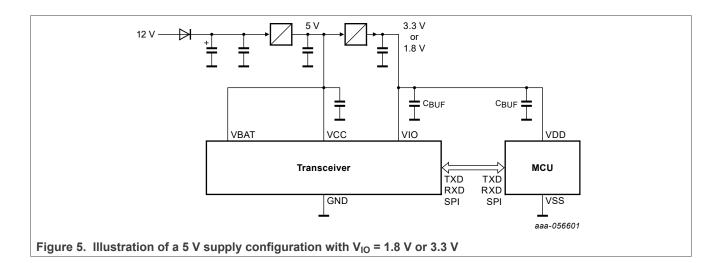

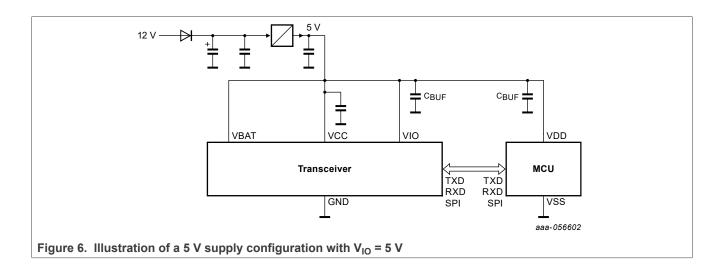

<u>Figure 3</u> through <u>Figure 6</u> illustrate power supply configuration examples for the four use cases listed in <u>Table 2</u>. See also <u>Section 3.6.1</u> on initializing bit VBATVCC for the chosen configuration.

| Table 2. | Power | supply      | configuration | examples   |

|----------|-------|-------------|---------------|------------|

|          |       | o a p p i j | oomgaration   | 0/10/10/00 |

| MCU supply     | V <sub>BAT</sub> = 12 V | $V_{BAT} = V_{CC} (5 V)$ |

|----------------|-------------------------|--------------------------|

| 3.3 V or 1.8 V | Figure 3                | Figure 5                 |

| 5 V            | Figure 4                | Figure 6                 |

# **NXP Semiconductors**

# AN14388

### TJA1445, TJA1465 application note

### 2.1.2 Battery reverse-polarity protection, filter and clamping circuitry

The circuitry for rectifying and filtering the car battery supply must ensure that  $V_{BAT}$  remains within the boundaries specified in the limiting values section of the data sheet. Any application circuitry that may generate transients on the battery supply, such as electric motors, must be supplied through a separate path without sharing the polarity protection diode connected to the transceiver. As a rule of thumb, the slew rate of the supply voltage on pin VBAT should be limited to less than 10 V/µs for rising edge and less than 1 V/µs for falling edge.

The internal soft clamp on pin VBAT can be turned off to minimize quiescent current while  $V_{BAT}$  is between 28 V and 40 V. External circuitry may need to be added to ensure that  $V_{BAT}$  does not exceed 40 V.

### 2.1.3 Capacitors

An external ceramic (i.e. low-ESR) buffer capacitor ( $C_{BUF}$ ) should be placed close to each supply pin to compensate for supply line inductance. When multiple supply pins are connected to the same power rail, they may share a common capacitor. The nominal capacitance on the VCC pin should be at least 1  $\mu$ F.

Ceramic capacitors connected to the car battery without current-limiting circuitry should have fail-safe properties (e.g. so-called 'Open-mode' or 'Soft-termination' capacitors). Alternatively, two conventional ceramic capacitors in series can be used, mounted on the PCB at a 90° angle relative to each other. Both options reduce the risk that bending the PCB could damage the capacitor in a way that causes it to conduct a high DC current. For details, contact the capacitor vendor.

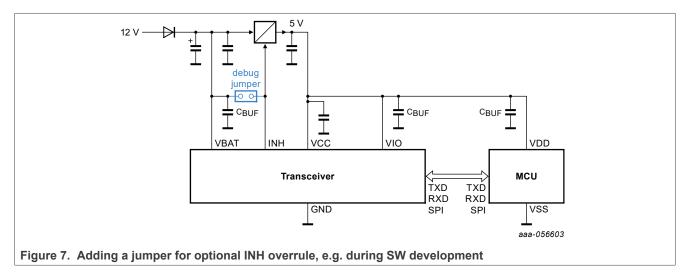

### 2.1.4 Auxiliary circuitry for debugging

When INH is used for direct on/off control of the voltage regulator supplying the MCU, consider adding optional circuitry to allow the regulator to be enabled continuously, regardless of the state of INH. An example is illustrated in <u>Figure 7</u>. Setting the debug jumper may be useful while a debugger or flash tool is connected to the MCU.

# 2.2 MCU/host controller interface

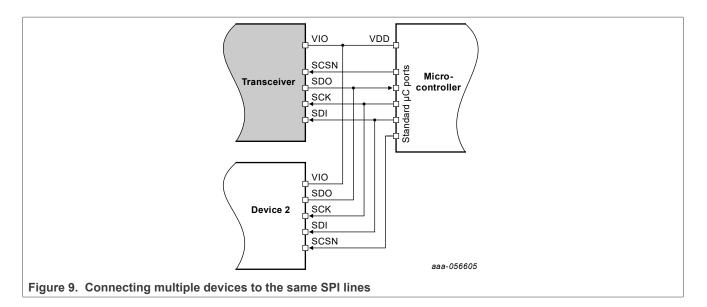

Six microcontroller port pins are needed to interconnect with the transceiver (4 SPI signals and the CAN TXD/ RXD signals), of which three (SCK, SDI and SDO) can be shared with other devices.

The  $V_{DD}$  supply for the MCU port pins connected to the transceiver must be identical to the transceiver  $V_{IO}$  supply.

### 2.2.1 SPI pins SCSN, SCK, SDI, SDO

The SPI interface is the main communication channel between the transceiver and the microcontroller. The microcontroller uses the SPI interface to configure the transceiver and to read back status information. SPI clock speed is up to 4 Mbit/s.

The transceiver is controlled via the 4-wire SPI interface as shown in <u>Figure 8</u>. It consists of four digital pins used for synchronization and data transfer:

- SCSN: SPI chip-select input (active-LOW)

- SCK: SPI clock input

- · SDI: SPI data input

- SDO: SPI data output

Pay particular attention to the routing of the clock signal and its ground return path because strong ringing or glitches due to crosstalk from other signals could cause problems. The greater the distance between the host controller and the transceiver, the more likely are the SPI signals to show some ringing during/after each edge. This should be avoided, especially for the SCK signal. Ringing can be reduced by placing series resistors close to the output terminals (see Figure 8). The sum of the resistor value and the source impedance should match the signal impedance on the PCB. A 100  $\Omega$  resistor is often appropriate. While higher values would further reduce ringing by slowing the edges, signal speed could be compromised. Note that maximum values are specified for SCK rise and fall times (t<sub>r(clk</sub>)/t<sub>f(clk)</sub>) and a minimum value for the delay time from SCK LOW to SCSN LOW (t<sub>d(SCKL-SCSNL)</sub>).

|                            | TJA1445<br>TJA1465  | VIO<br>SCSN<br>SCK<br>SDI<br>SDO <sup>100 Ω<sup>(1)</sup><br/>GND</sup> | 100 Ω <sup>(1)</sup><br>100 Ω <sup>(1)</sup><br>100 Ω <sup>(1)</sup><br>100 Ω <sup>(1)</sup> | Microcontroller |  |

|----------------------------|---------------------|-------------------------------------------------------------------------|----------------------------------------------------------------------------------------------|-----------------|--|

| (1) Optional series resist | ors to reduce ringi | ng                                                                      |                                                                                              | aaa-056604      |  |

When the input function of the microcontroller port pin connected to SDO remains active in a low-power mode, the SDO signal must be pulled HIGH or LOW - using an external resistor or by activating an MCU-internal pull-

up or pull-down resistor. Internal pull-up resistors on pins SDI and SCK are turned on automatically when a HIGH level is applied externally; internal pull-down resistors are turned on when a LOW level is applied. When not driven by an external signal, the pins retain the most recently selected state (HIGH or LOW). To avoid compromising this functionality, external pull-up or pull-down resistors should not be added. While in a low-power mode, the

The MCU may share the signals connected to SCK, SDI and SDO with other peripheral devices, but the transceiver needs its own chip-select signal, SCSN (see <u>Figure 9</u>). Daisy-chain connections of SDI and SDO with other devices are not supported.

related MCU port pins should remain on or off without pull-up or pull-down currents.

# AN14388

### TJA1445, TJA1465 application note

# 2.2.2 CAN TXD/RXD

The CAN bit stream input (TXD) and output (RXD) pins must be connected to the corresponding MCU port pins. TXD is connected to the MCU port pin with CAN protocol controller bit stream output function 'TXD' (or a similar name). RXD is connected to the MCU port pin with CAN protocol controller bit stream input function 'RXD' (or a similar name).

While series resistors could be added to reduce ringing and emissions on these signals, they could have a negative impact on the loop delay. Refer to the OEM hardware specifications for advice on adding such components.

# 2.2.2.1 Optional second pair of TXD/RXD pins (TJA1445B/TJA1465B only)

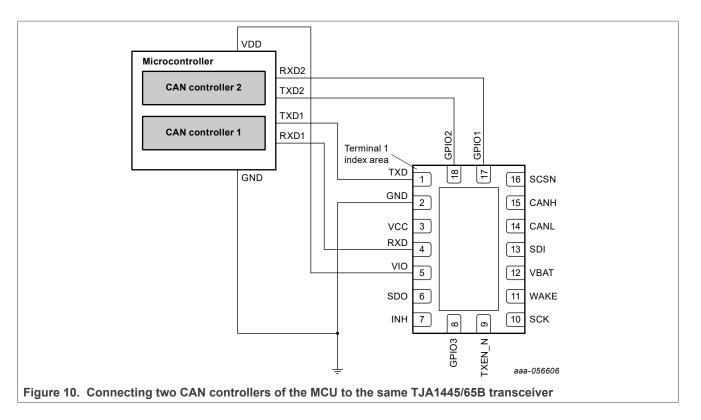

When the MCU has more than one CAN protocol controller but the message buffer of a single controller is not big enough for the application, two CAN protocol controllers can be connected to a single transceiver, as illustrated in Figure 10.

- One of the CAN controllers is mapped to the MCU TXD/RXD port pins connected to TXD/RXD on the transceiver

- The other CAN controller is mapped to the MCU TXD/RXD pins connected to GPIO2 (with TXD2 function selected) and GPIO1 (with RXD2 function selected)

The corresponding GPIO1/2 pin configuration is explained in <u>Section 3.6.4</u>.

# **NXP Semiconductors**

# AN14388

TJA1445, TJA1465 application note

# 2.2.3 TXEN\_N (TJA1445B/TJA1465B only)

The CAN transmitter is disabled when pin TXEN\_N is HIGH. In Normal, Standby, Sleep and ListenOnly modes, TXEN\_N is pulled HIGH internally via a soft pull-up. In all other modes, it may be driven LOW internally (sufficient supply conditions on pin VBAT and/or VIO required). It must be driven LOW externally to enable the CAN transmitter. The output driver characteristics of external circuitry connected to this pin should be 'low-side open-drain', with or without soft pull-up.

The transmitter is turned off when the transceiver is in Standby or Sleep mode, regardless of the level on TXEN\_N. However, if  $V_{IO}$  remains powered while the transceiver is in a low-power mode, TXEN\_N should not be driven LOW externally as the internal pull-up resistance on the pin would cause an increase in quiescent current.

When TXEN\_N functionality is not needed, the level on pin TXEN\_N pin must still be determined via external hardware, depending on the V<sub>IO</sub> supply conditions in Sleep and Standby modes:

- If V<sub>IO</sub> is turned off while the transceiver is in a low-power mode, the TXEN N pin may be hardwired to ground.

- If V<sub>IO</sub> remains active while the transceiver is in a low-power mode, TXEN\_N should only be driven LOW when the transceiver is in Normal or ListenOnly mode. Otherwise, quiescent current will be increased due to the internal pull-up resistance on TXEN\_N. For example, connect TXEN\_N to its neighbor pin GPIO3 to control GPIO3 when an MCU pin is not available for this (see also Section 2.2.4, Section 3.7.3 and Section 3.8.2).

### 2.2.4 GPIO pins (TJA1445B/TJA1465B only)

The TJA1445/65B variants contain three GPIO pins that can be used by the microcontroller as extra SPIcontrolled remote digital I/O port pins.

They can be used to help minimize the bottom-line MCU port pin 'consumption' by the transceiver. When needed, a signal connected to a GPIO pin may be used to wake up the MCU from a low-power state (see

<u>Section 3.6.4</u>). However, GPIO pin functionality is only available when the transceiver is in Normal, Standby, Sleep or ListenOnly mode and  $V_{IO}$  is present.

When a GPIO pin is not used, it can be left unconnected thanks to its internal repeater function (automatic pullup/down resistor).

See also <u>Section 2.2.2.1</u> on using GPIO pins as a second TXD/RXD signal pair.

# 2.3 CAN bus connection to CANH, CANL

### 2.3.1 CAN bus termination

In general, the termination circuitry on the CAN bus should be designed according to the car manufacturer's specifications. If this is not applicable, refer to NXP application hints document 'Rules and Recommendations for In-vehicle CAN Networks' [3].

### 2.3.2 CAN ESD protection

Although the CANH/CANL bus pins are equipped with internal ESD protection, adding external clamping components can be considered, e.g. PESD2CANFD24V-T or PESD2CANFD24L-T.

# 2.4 WAKE pin interface

In general, on-board circuitry must ensure that the WAKE pin is operated within the boundaries specified in the Limiting values section of the data sheet. The example circuits in this section may need to be adapted to the specific conditions of the application.

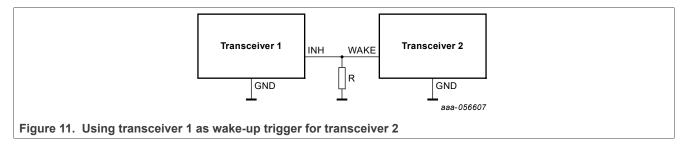

### 2.4.1 WAKE pin connected to the INH pin on another transceiver

An example circuit showing the INH pin on one transceiver being used as a wake-up source for another transceiver is illustrated in Figure 11. With the INH pin on transceiver 1 turned off in Sleep mode, resistor R pulls the WAKE pin on transceiver 2 LOW. When Transceiver 1 wakes up from Sleep mode, the INH output turns on automatically, creating a rising edge on the WAKE input on transceiver 2. The value of resistor R must be high enough to ensure that the INH output is not overloaded and low enough to achieve a LOW level while the internal pull-up on the WAKE pin is active.

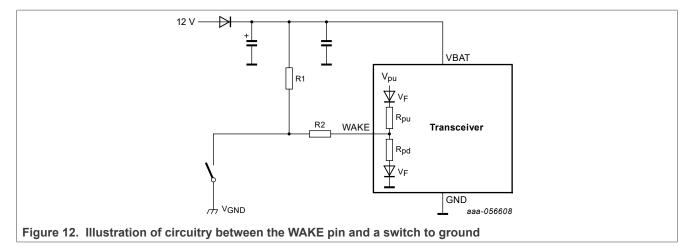

### 2.4.2 WAKE pin connected to external switch to ground

In the example circuit in Figure 12, a switch or button with a ground connection serves as the wake source. Resistor R1 determines the WAKE signal level while the contact is open. R2 is needed to protect the WAKE pin against ESD events applied to the switch cable. The minimum value of R2 (3 k $\Omega$ ) can be derived from the ESD test conditions specified in the Limiting values section of the data sheet. Note that the R2 package must be large enough to prevent arcing over its terminals during an ESD event.

# AN14388

TJA1445, TJA1465 application note

The value of R1 determines the current running through the closed contact of the switch.

The sum of R1 and R2 must be low enough to maintain a HIGH level on the WAKE pin while it is being pulled down internally via  $R_{pd}$ :

$$\begin{split} &V_{th(wake)} < V_F + (V_{BAT} - V_F) \ x \ R_{pd} \ / \ (R_{pd} + R2 + R1) \\ &V_{th(wake)} \ x \ (R_{pd} + R2 + R1) < V_F \ x \ (R_{pd} + R2 + R1) + (V_{BAT} - V_F) \ x \ R_{pd} \\ &(V_{th(wake)} - V_F) \ x \ (R_{pd} + R2 + R1) < (V_{BAT} - V_F) \ x \ R_{pd} \\ &R_{pd} + R2 + R1 < ((V_{BAT} - V_F) \ / \ (V_{th(wake)} - V_F)) \ x \ R_{pd} \end{split}$$

R1 + R2 <  $R_{pd} x ((V_{BAT} - V_F) / (V_{th(wake)} - V_F) - 1)$

Obviously, the requirement for the sum of R1 and R2 depends on the supply voltage connected to R1 (here  $V_{BAT}$ ), and this voltage must be higher than the threshold voltage  $V_{th(wake)}$  at the WAKE pin. For example, for the circuitry to work correctly when  $V_{BAT}$  = 4.25 V or higher and  $V_{th(wake)max}$  = 2.6 V,  $V_F$  = 0.3 V and  $R_{pd(min)}$  = 100 k $\Omega$ , the requirement would be:

R1 + R2 < 100 k $\Omega$  x ((4.25 - 0.3) / (2.6 - 0.3) - 1) = 100 k $\Omega$  x (3.95/2.3 -1) = 71 k $\Omega$

R2 must be low enough to guarantee a LOW level on the WAKE pin while it is being pulled up internally via  $R_{pu}$ , considering there may be an offset  $V_{GND}$  between switch ground and module ground.

$V_{th(wake)} > V_{GND} + R2 / (R2 + R_{pu}) \times (V_{pu} - V_F - V_{GND})$   $R2 / (R2 + R_{pu}) < (V_{th(wake)} - V_{GND}) / (V_{pu} - V_F - V_{GND})$   $With V_R = (V_{th(wake)} - V_{GND}) / (V_{pu} - V_F - V_{GND}):$   $R2 / (R2 + R_{pu}) < V_R$   $R2 < R2 \times V_R + R_{pu} \times V_R$   $R2 < R2 \times V_R + R_{pu} \times V_R$   $R2 \times (1 - V_R) < R_{pu} \times V_R$   $R2 < R_{pu} \times V_R / (1 - V_R)$   $With V_{th(wake)} = 1.8 \text{ V}, V_{GND} = 1 \text{ V}, V_{pu} = 5.5 \text{ V}, V_F = 0.3 \text{ V} \text{ and } R_{pu} = 100 \text{ k}\Omega, \text{ R2 is calculated as: }$

For example, the above requirements can be met with R2 = 10 k $\Omega$  for ESD protection and R1 = 1.2 k $\Omega$  for 10 mA contact current at 12 V.

R2 < 23.5 kΩ

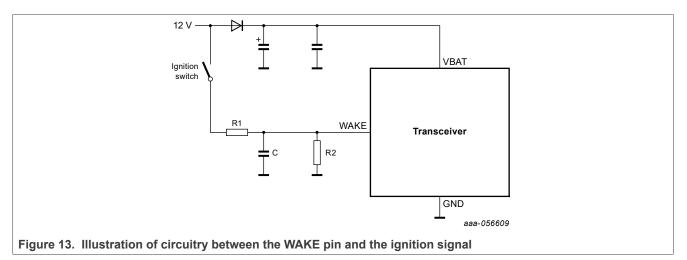

### 2.4.3 WAKE pin connected to ignition

<u>Figure 13</u> illustrates an interconnection between the WAKE pin and the ignition line (aka 'terminal 15') of the car. R2 ensures that a LOW level is detected when the switch is open. R2 can be calculated as described in <u>Section 2.4.2</u>, with  $V_{GND} = 0$  V. With  $V_{th(wake)} = 1.8$  V,  $V_{GND} = 0$  V,  $V_{pu} = 5.2$  V,  $V_F = 0.3$  V and  $R_{pu} = 100$  k $\Omega$ :

R2 < 58 k $\Omega$   $\rightarrow$  select 51 k $\Omega$ .

The combination of R1 and C acts as a low-pass filter to suppress transients on the battery line. The selected capacitance should be large enough to keep the WAKE pin voltage within specified limits while storing the charge of an ESD event. For example, when a 150 pF capacitor with 8 kV discharges into a previously empty 47 nF capacitor, the resulting voltage would be 39.4 V on both capacitors. For an additional safety margin and to compensate for tolerances, a nominal 100 nF capacitor may be selected for C in this example.

When the switch is closed, the value of R1 should be calculated to guarantee a HIGH level on the WAKE pin while it being pulled down internally via  $R_{pd}$  and externally via R2.

The formula used in Section 2.4.2 to calculate R1 + R2 can be reused to calculate R1. When using the same parameters for V<sub>BAT</sub> and V<sub>th(wake)</sub> (V<sub>BAT</sub> = 4 V or higher and V<sub>th(wake)</sub> = 2.6 V) but with R<sub>pd</sub> = 34 k $\Omega$  (internal 100 k $\Omega$  resistor R<sub>pd</sub> in parallel with external 51 k $\Omega$  resistor R2) and V<sub>F</sub> = 0 V (which simplifies the calculation and creates an additional safety margin), the requirement would be:

R1 < 34 k $\Omega$  x (4 / 2.6 - 1) = 18.3 k $\Omega$   $\rightarrow$  select 18 k $\Omega$ .

The resulting RC filter time constant would be  $18 \text{ k}\Omega \times 100 \text{ nF} = 1.8 \text{ ms}$ . When a longer filter time is needed, increase the capacitance, because the resistance should not exceed the calculated value.

# 3 Application software

This section proposes ways a microcontroller (MCU) can use application software to control the transceiver via the SPI. It assumes that the interconnections between the transceiver and the MCU are available, as discussed in Section 2.2. For aspects related to functional safety, see the related safety manual <sup>[4]</sup>.

# 3.1 SPI status check

SPI communication with the transceiver is only possible once the device has powered up. Depending on the power supply architecture of the module, low battery conditions may exist under which the MCU may be running while the transceiver is in an unpowered state. This condition can be detected by comparing the first two return bytes of an SPI transfer with the corresponding bytes sent to the transceiver. A mismatch indicates that the

Application note

AN14388

transceiver is not ready for SPI communication. This check should always be performed when attempting to read data from the device registers to confirm that the received data is valid.

# 3.2 Addressing multiple registers at once via SPI

The transceiver accepts SPI messages with up to four bytes of data for read and/or write access. In this way, up to four registers with incremental addresses can be accessed with a single SPI message. The address carried by the SPI frame points to the register with the first (lowest) address (see example in <u>Section 3.6.4</u>, <u>Table 4</u> describing writing to addresses 0x042 and 0x043). The register map is optimized to use this feature effectively, with functionalities such as PN configuration, status information or configuration bits grouped accordingly. Refer to the data sheet for further details on the SPI protocol and register map.

# 3.3 Parity bit

The parity bit, PAR, is calculated in the user application. The first 16 SPI bits must contain an even number of '1' bits - so if the first 15 bits contain an odd number of 1's, the parity bit (bit 16) must be set to 1 (otherwise it is set to 0).

### 3.4 Read-back of written data

Bit failures on the SDI signal occurring during transmission of one or more data bytes of an SPI frame will not be detected by the device. To be on the safe side, writing to registers should consist of:

- an initial SPI frame writing to a register(s)

- a second SPI frame reading the register contents (same address but with read-only bit set)

- a comparison between transmitted (1st frame) and read data (2nd frame)

When a match is confirmed and the SPI status check (see <u>Section 3.1</u>) is ok, the write attempt can be regarded as successful. Otherwise, the write and check should be repeated. An escape mechanism should be implemented to prevent it being stuck in an endless loop.

Checking for a match between read and written data does not apply to Interrupt status registers, to the System reset register or to read-only bits in registers. When an attempt to set the WDD and/or the WDOFF bit to '1' in the Watchdog configuration register fails, this does not necessarily mean that the SPI transfer has failed. These bits can be set to '1' only when the device is in an appropriate state, as described in the data sheet.

Note that the SPI supports full-duplex communication, but an SPI frame writing new data to a register returns the data the register had before the new data arrived.

### 3.5 First SPI interaction after power up or wake-up from Sleep

The first SPI interaction with the device (reading or writing to/from at least one register) should occur within  $t_{to(MCU)}$  (the MCU reaction timeout time) after power up or wake-up from Sleep mode. If the SPI interaction does not happen in time, the device will enter Sleep mode with remote (CAN bus) and local (WAKE pin) wake-up sources enabled. This behavior is good for handling MCU malfunctions by:

• minimizing battery draining while the car is parked (i.e. while there is no CAN bus or WAKE signal activity)

• retrying MCU recovery whenever there is activity on the CAN bus or on the WAKE pin

The MCU reaction timeout time is fixed for power up, but it can be shortened for Sleep mode by setting LUVIOSEL = 0 (note that the long undervoltage detection time  $t_{det(uv)long}$  will also be shortened).

# 3.6 Device initialization

### 3.6.1 Power supply configuration

When pin VBAT is supplied with the same 5 V voltage as pin VCC (see <u>Figure 5</u>, <u>Figure 6</u>), or with any other regulated voltage < 5.5 V, bit VBATVCC in the system configuration register must be set to 1 and  $V_{CC}$  must remain powered in low-power modes.

When  $V_{CC}$  is turned off in Sleep mode, VBATVCC must be cleared to 0 and  $V_{BAT}$  must be powered with 12 V (see <u>Figure 3</u> and <u>Figure 4</u>) or with a regulated voltage > 5.5 V. See <u>Table 3</u> for an overview of the available options.

#### Table 3. VBATVCC settings in Sleep mode

| V <sub>CC</sub> in Sleep mode | $V_{BAT} = V_{CC}^{[1]}$ | V <sub>BAT</sub> = 12 V (or regulated voltage > 5.5 V) <sup>[1]</sup> |

|-------------------------------|--------------------------|-----------------------------------------------------------------------|

| V <sub>CC</sub> on            | VBATVCC = 1              | VBATVCC = 0                                                           |

| V <sub>CC</sub> off           | not allowed              | VBATVCC = 0                                                           |

[1] V<sub>BAT</sub> must be powered in Sleep mode.

When an external clamping circuit is used on  $V_{BAT}$  (see <u>Section 2.1.2</u>), bit BCCTRL in the system configuration register may be set to 1 (internal clamp off) to reduce the internal quiescent current while  $V_{BAT}$  is above 28 V. Otherwise, BCCTRL must be cleared to 0 (internal clamp enabled).

The other bits in the system configuration register, RXDINTC (see <u>Section 3.6.5</u>) and LUVIOSEL (see <u>Section 3.5</u>), should be configured as required by the application.

### 3.6.2 CAN transceiver configuration

The default value of 0x00 for the CAN configuration register should be sufficient for sending and receiving CAN bus messages. Bit CWC may need to be adjusted for wake-up pattern optimization per OEM requirements.

When TXEN\_N (TJA1445B/65B only) is controlled by the MCU, it must be set LOW to enable the transmitter.

GPIO configuration for optional TXD2/RXD2 is discussed in Section 3.6.4.

### 3.6.3 Wake-up source configuration

Local (pin WAKE) and remote (CAN) wake-up can be enabled/disabled via interrupt enable bits WPRE/WPFE and CWE in the System interrupt enable register. This can be done during initialization or, at the latest, before the ECU enters a low-power mode. Note that these bits may have been set automatically by the device during earlier failure handling (VIO undervoltage or MCU reaction timeout).

When the transceiver switches off power to the MCU in Sleep mode via the INH pin (see <u>Figure 3</u> and <u>Figure 4</u>), consider keeping 'regular' wake-up sources (CAN and WAKE pin) disabled until just before issuing a Sleep command. This ensures that any accidental Sleep command (e.g. due to noisy SPI) would only trigger an SPI fail interrupt (if enabled) and not an unintended transition to Sleep mode.

When partial networking (PN) wake-up is employed, it must be configured via the PN ID, PN ID mask, PN frame control and PN data rate and filter configuration registers. When the data length code (DLC) and data field are included in the wake-up frame (PNDM = 1), the DLC and the PN data mask registers need to be initialized as well. PN configuration is completed by writing CPNC = 1 and PNCOK = 1 to the PN CAN configuration register. With the same SPI command, the desired behavior for CAN FD frames or CAN XL frames should be selected via bits PNECC and CXLDE (if applicable to the device variant). A detailed explanation of the PN settings is provided in the appendix, <u>Section 4.1</u>. SPI commands for an example PN configuration with transition to Sleep mode are described in the appendix, <u>Section 4.2</u>.

Bit WFC in the wake-up pulse configuration register can be used to select one of two filter times (short or long) for the WAKE pin.

### 3.6.4 GPIO pin configuration (TJA1445B / TJA1465B only)

When GPIO pins are used, their functionality needs to be initialized via bits GPIOxC and GPIOxFS in the GPIOx configuration registers (x = 1, 2, 3). The digital input function is always available, independent of the function selected via GPIOxFS. For example, select GPIOxFS = 0x02 to use the pin as a general-purpose, bi-directional remote I/O port (see also Section 2.2.4).

For pins with an output function other than RXD2, the polarity needs to be defined via bits GPPx in the GPIO polarity configuration register. These bits may also be used to initialize the default level on GPIO pins used as digital outputs (see also <u>Section 3.7.3</u>).

When a GPIOx pin is to be used as a wake-up interrupt source, it must be configured with GPIOxFS = 0x13, 0x14 or 0x15 (wake-up detection input with rising, falling or dual-edge sensitivity) and with GPIOxE = 1 (interrupt enabled). The configuration combination GPIOxFS = 0x01 ('digital input only') with GPIOxE = 1 will not configure the pin for wake-up detection.

Using GPIO1/2 as a second pair of TXD/RXD pins to connect with a second CAN controller is discussed in <u>Section 2.2.2.1</u>. The construction of a single SPI frame to configure the GPIO pins for this purpose is illustrated in <u>Table 4</u>.

| SPI header |           |           |        | GPIO1 config register<br>(address 0x042) |                      | GPIO2 config register<br>(address 0x043) |      |                  |       |      |

|------------|-----------|-----------|--------|------------------------------------------|----------------------|------------------------------------------|------|------------------|-------|------|

| ADDI       | RESS      | RO        | PLS    | PAR                                      |                      | DATA0                                    |      |                  | DATA1 |      |

|            | ess of    | not read- | 2 data | parity                                   | GPIO1C               | GPIO1FS                                  |      | GPIO2C           | GPI   | D2FS |

| GPIO1 c    | onfig reg | only      | bytes  |                                          | output:<br>push-pull | RXD2 (and RXD)                           |      | input<br>pull-up |       |      |

| 0x         | 42        | 0         | 01     | 1                                        | 000                  | 0x                                       | 06   | 001              | 0×    | :05  |

| 0x04       | 0x02      | 0         | 01     | 1                                        | 000                  | 0                                        | 0110 | 001              | 0     | 0101 |

| Byte 1     |           | Byt       | e 2    |                                          | Byte 3               |                                          |      | Byte 4           |       |      |

| 0x04       | 0x04 0x23 |           |        |                                          | 0x06                 |                                          |      | 0x25             |       |      |

Table 4. Initialization of GPIO1/2 as RXD2/TXD2, using a single SPI frame

### 3.6.5 Configuring interrupts

Transient events on internal or external signals may be interpreted as interrupts when related interrupts have been enabled. Some of these interrupts can be used as wake-up sources (see <u>Section 3.6.3</u>).

When an interrupt is generated by the transceiver in Standby or Sleep mode, it is signaled to the MCU via a LOW level on pin RXD while  $V_{IO}$  is available. It is possible to select which interrupts are signaled on RXD via the RXDINTC bit in the system configuration register. When RXDINTC = 0 (default value), only wake-up and power-on interrupts are signaled on RXD. When RXDINTC = 1, any enabled interrupt will be signaled on RXD and will wake the MCU from its low-power mode (applicable when the MCU remains powered, see Section 3.8.2).

Transceiver interrupts may already be pending after an MCU reset, even before they have been enabled during the initialization process. For example, the non-maskable PO interrupt is always generated during power on. An MCU reset due to wake-up from Sleep mode would be accompanied by a pending wake-up interrupt of the transceiver. See also <u>Section 3.7.2</u>.

Note that the device may already be in Normal mode if it was powered up with a steadily dominant CAN bus. See also <u>Section 4.3.2</u>.

### 3.6.6 Transition to Normal mode

The CAN transceiver is only enabled for full operation after the device has entered Normal mode. Provided  $V_{CC}$  is present, this will happen  $t_{t(moch)}$  after issuing the Normal mode command (write 0x0F to the Mode control register).

# 3.7 Normal operation

### 3.7.1 Confirmation of transceiver status

Once initialized (Section 3.6), the transceiver should be ready for CAN communication. However, software should re-confirm this whenever CAN communication fails and also on a regular basis with an interval shorter than the MCU reaction timeout time  $t_{to(MCU)}$ . This is necessary because certain  $V_{BAT}$  undervoltage conditions may reset the transceiver without resetting the MCU. The CTS bit in the CAN status register indicates whether the transceiver is up and running (CTS = 1) or is not active (CTS = 0). When reading CTS returns 0, a device re-initialization may be needed. If this was caused by a persistent undervoltage, however, it may need to be repeated multiple times until the battery voltage has recovered sufficiently. See also Section 3.1 and Section 3.5.

### 3.7.2 Interrupt handling

While the device is in Normal mode, enabled interrupts are still generated but they are not signaled on pin RXD. The MCU may check periodically for pending interrupts by reading the interrupt status registers. This can be done most efficiently with a single 6-byte SPI read access to address 0x060 (the system interrupt status register). For the TJA1445A/TJA1465A, a 5-byte access to the same address is sufficient. If any of the returned data bytes is not 0x00, there is a pending interrupt.

Once processed, single or multiple interrupts can be cleared, individually or all at once, by writing 1 to the associated bits in the interrupt status registers.

# 3.7.3 Using GPIO pins as remote digital I/O port pins (TJA1445B/TJA1465B only)

The output level on a GPIO pin configured as a 'digital output' (GPIOxFS = 0x02) is controlled via the GPPx bits in the GPIO polarity configuration register. Since this register is common to all three GPIO pins, changing the output level of one pin means that the existing polarity configuration of the other pins needs to be repeated.

The HIGH/LOW status of a GPIO output or input signal can be sampled by reading the GPIO/TXEN\_N status register. When a GPIO pin was configured as a wake-up input with enabled interrupt (see <u>Section 3.6.4</u>), the occurrence of edges that have passed the input filter with the selected polarity will be visible in the GPIO interrupt status register.

# 3.8 Transition to low-power mode

If not yet done, the required wake sources must be enabled before the ECU enters a low-power mode (see <u>Section 3.6.3</u>), and all pending interrupts should be processed and cleared (see <u>Section 3.7.2</u>). Note that the transceiver will not enter Sleep mode unless at least one of the main wake-up sources (CAN bus, WAKE pin) is enabled and all wake-up interrupts are cleared. Entering Standby mode is always possible, even without any wake source being enabled.

Before leaving transceiver Normal mode, consider waiting until ongoing CAN bus message transmission or reception has been completed.

### 3.8.1 Sleep mode (MCU not powered in low-power mode)

When turning off the MCU supply via the INH signal in Sleep mode (Figure 3, Figure 4, Figure 7), consider the capacitor discharge time. After transmitting the SPI Sleep mode command (write 0x01 to the Mode control register), wait long enough for the MCU to power down. During this time, the device Sleep status can be confirmed via the Mode status register, i.e. the device can be checked for coincidental wake-up. If the MCU is still running even though the transceiver is in Sleep mode, this would indicate a HW error preventing the voltage regulator being shut down via the INH signal. Allow  $t_{t(moch)}$  between issuing the SPI sleep command and confirmation via the Mode status register. See Appendix Section 4.2 for an example SPI command sequence for PN configuration with transition to Sleep mode.

See Appendix <u>Section 4.2</u> for an example SPI command sequence for PN configuration with transition to Sleep mode.

### 3.8.2 Standby mode (MCU remains powered in low-power mode)

When the MCU remains powered in low-power mode, the RXD signal is used to wake the MCU from its lowpower mode ('MCU stopped'). In transceiver Standby mode (write 0x06 to the Mode control register), RXD is LOW continuously while interrupts are pending (as selected via bit RXDINTC, see also <u>Section 3.6.5</u>).

When the related MCU pin interrupt is edge-sensitive, the readiness of the transceiver to generate a wake-up edge on RXD must be confirmed before stopping the MCU: the RXD signal must be HIGH. If it is LOW, there are pending interrupts that need to be cleared (see <u>Section 3.7.2</u>) before the MCU is stopped.

For the TJA1445B or TJA1465B, TXEN\_N should not be driven LOW in a low-power mode. Otherwise, the internal pullup resistance on the pin would increase the quiescent current (see also <u>Section 2.2.3</u>).

### 3.9 Wake-up

After the MCU wakes up from low-power mode (Section 3.8.2), or after an MCU reset caused by a wake-up from Sleep mode (Section 3.8.1), a full re-initialization of the transceiver (Section 3.6) may not be necessary but is recommended to be on the safe side. In any case, a transition to Normal mode (Section 3.6.6) will need to be executed before normal operation can be resumed. Remember that the first SPI interaction with the device should occur within  $t_{to(MCU)}$ , the MCU reaction timeout time, after a wake-up from Sleep mode.

# 4 Appendix

### 4.1 Partial networking configuration

Since the proper configuration of the partial networking registers is critical for successful wake-up from low-power mode, the integrity of any write access to these registers should be checked as described in <u>Section 3.1</u> and <u>Section 3.4</u>.

### 4.1.1 Concept of selective wake-up

Partial networking is the concept of splitting the network into subnetworks that can be woken-up separately by dedicated wake-up frames (WUFs). Such subnetworks can contain any number of nodes - even a single node or all the nodes on the network. A node may belong to more than one subnetwork. The network owner needs to define how this selective wake-up of the subnetworks by WUFs is handled.

A WUF is a standard CAN frame according to ISO11898-1 and therefore consists of the CAN identifier (ID, Standard or Extended Frame Format), the data length code (DLC) and the data field of a CAN frame. Three options are available for defining which of these elements is to be used to control the wake-up of subnetworks:

• Only the ID

- ID and DLC with DLC = 0

- ID, DLC with DLC > 0 and data field

Note that a WUF frame with CAN FD or CAN XL frame format is not supported, even when PNDM = 0.

### 4.1.2 ID and ID mask

The CAN frame identifier (ID) that will be accepted as a valid WUF ID is defined in the partial networking ID registers.

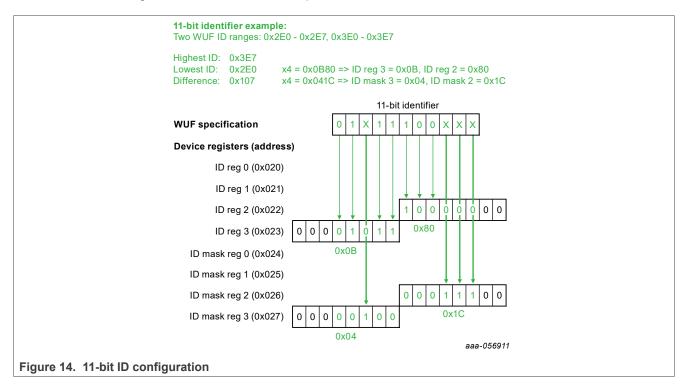

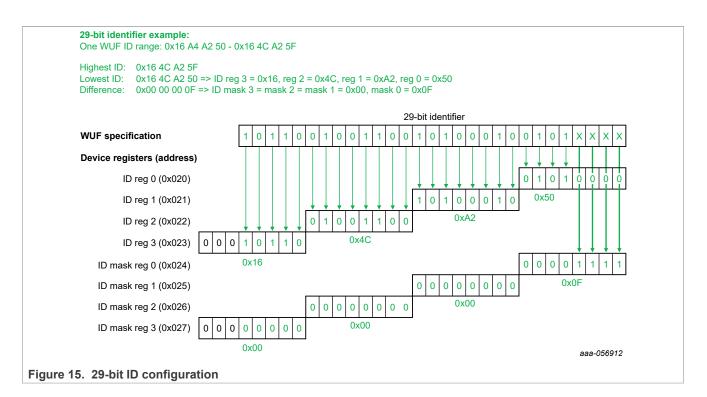

As illustrated in Figure 14, an 11-bit ID can be loaded into ID registers 3 and 2 after shifting the ID to the left by two bit positions, which is equivalent to multiplying it by 4. A 29-bit identifier can be loaded directly into ID registers 3 to 0 (see Figure 15).

For 11-bit IDs, the values stored in ID registers 1 and 0 are not used and are 'don't care'.

If only one CAN ID is used for wake-up, then all partial networking ID mask registers should be set to 0x00 (default value). As specified by ISO11898-2, multiple WUF IDs can be configured by defining individual ID bits as 'don't care', which is represented by an 'x' in the WUF ID examples in <u>Figure 14</u> and <u>Figure 15</u>. A '1' needs to be set at the corresponding bit positions in the ID mask. The ID mask can also be calculated as follows:

- 1. Determine the highest ID by setting all 'don't care' bits to '1'

- 2. Determine the lowest ID by setting all 'don't care' bits to '0'

- 3. The difference, highest ID minus lowest ID, represents the ID mask value

# AN14388

### TJA1445, TJA1465 application note

### 4.1.3 DLC and data mask

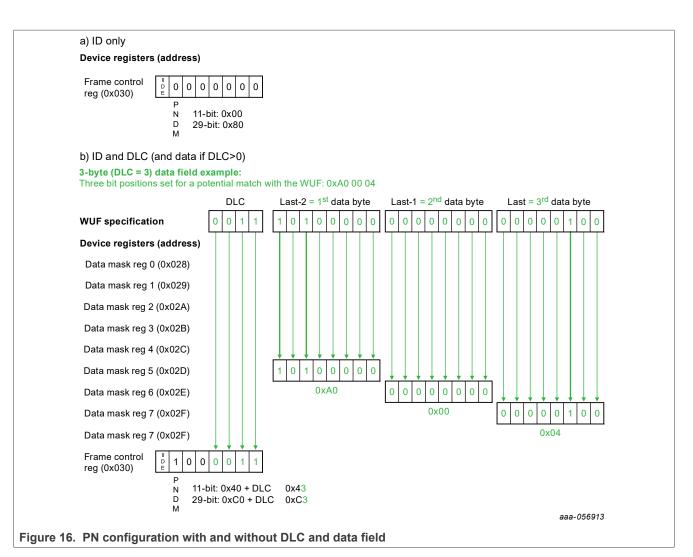

If a wake-up has already been triggered when the received identifier was found to match the configuration, regardless of the DLC and data field contents (Figure 16), the appropriate contents for the frame control register is 0x00 for 11-bit WUF, or 0x80 for 29-bit WUF. Further configuration of data length code (DLC) or data mask is not needed in this case.

When the data field of the WUF is to be included for wake-up selection, each '1' bit in the data field is supposed to address a group of network nodes. A WUF may address multiple groups by setting multiple bits in the data field to '1'. In turn, a PN transceiver may be assigned to several groups by setting the corresponding bits in the data mask registers to '1'. Then a PN transceiver only wakes up when:

- the ID of the WUF matches with the configuration as explained in Section 4.1.2

- · and the WUF DLC matches the DLC in the frame control register

- and the WUF has a '1' in one or more data field bit positions for which the transceiver has set the corresponding bits in the data mask registers to '1'.

The appropriate configuration of the frame control and data mask registers for an example with WUF DLC = 3 is illustrated in Figure 16.

### 4.1.4 Data rate

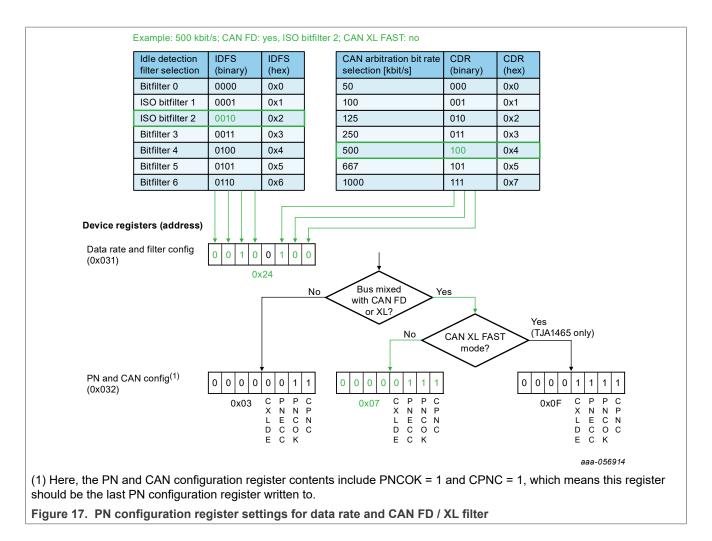

To decode the incoming classic CAN frame correctly, its bit rate must be defined via the CDR bits in the partial networking data rate and filter configuration register (address 0x031). In the example shown in <u>Figure 17</u>, the selected data rate is 500 kbit/s.

### 4.1.5 Optional CAN FD/CAN XL and FAST mode tolerance

When one of the other CAN frame formats, CAN FD or CAN XL, is expected to appear on the bus, the 'CAN FD passive' feature must be enabled by setting PNECC = 1 (in the partial networking and CAN configuration register). Note that the TJA1465 is the recommended product for CAN XL tolerance.

The PN decoder is not able to read the data phase of a CAN FD or CAN XL frame. When the PN passive function has recognized the FD or XL format of a CAN frame, it skips the rest of that frame by waiting for the bus to become idle (continuously recessive bus state for between 6 and 10 arbitration data rate bit times).

The FD passive function features a number of digital filter characteristics supporting the idle detection mechanism, including the two bitfilter options specified in ISO11898-2. Such a filter should reject 'noise', which is defined as dominant pulses shorter than would be expected in a CAN message (including CAN FD or CAN XL, if applicable). For example, the expected nominal minimum pulse length is 500 ns for 2 Mbit/s, 200 ns for 5 Mbit/s and 125 ns for 8 Mbit/s. The maximum value of the selected filter time t<sub>fltr(bit)dom</sub> must be lower than

these pulse lengths, considering device tolerances and effects of bus physics. The bit filter requirements should ideally be defined by the system owner.

The ISO11898 filter options are defined as percentages of the arbitration bit time, which is the reciprocal of the chosen arbitration bit rate defined via the CDR. These filters should be the first choice for CAN FD speeds up to 5 Mbit/s. Example: when CDR = 100 (arbitration bit rate = 500 kbit/s), ISO bit filter 2 ignores pulses up to 175 ns, making it suitable for a data phase bit rate up to 5 Mbit/s.

The filter options are set via the idle detection filter select bits (IDFS in the partial networking data rate and filter configuration register at address 0x031). In addition to the ISO filter options, the TJA1445/65 provides a number of filter options with settings specified as absolute values independent of the CDR settings (bit filter 3, for example, ignores pulses up to 93 ns, which makes it suitable for communication up to 8 Mbit/s).

The properties of the two ISO filter options (with absolute filter times calculated for an arbitration data rate of 500 kbit/s), along with bit filter 3, are summarized in <u>Table 5</u>. Pulses longer than the max bit filter time value are never rejected. Pulses shorter than the min bit filter time value are always rejected. Pulses with lengths between these values may, or may not, be rejected.

#### Table 5. IDFS examples

|                                  | ISO bit filter 1 (IDFS = 0x1)   | ISO bit filter 2 (IDFS = 0x2)   | Bit filter 3 (IDFS = 0x3) |

|----------------------------------|---------------------------------|---------------------------------|---------------------------|

| Min bit filter time              | 5 % (100 ns <sup>[1]</sup> )    | 2.5 % (50 ns <sup>[1]</sup> )   | 18 ns                     |

| Max bit filter time              | 17.5 % (350 ns <sup>[1]</sup> ) | 8.75 % (175 ns <sup>[1]</sup> ) | 93 ns                     |

| Max suitable data phase bit rate | 2 Mbit/s <sup>[1]</sup>         | 5 Mbit/s <sup>[1]</sup>         | 8 Mbit/s <sup>[2]</sup>   |

[1] This number is only valid for an arbitration data rate of 500 kbit/s (CDR = 100).

[2] Only applicable to the CAN SIC device.

With PNECC set to 1, a TJA1465 device tolerates not only CAN FD frames but also CAN XL frames sent in SIC mode. Only when CAN XL frames are sent using the FAST mode level scheme must bit CXLDE also be set to 1. As this function consumes additional current, it is recommended to disable it (CXLDE = 0) when not needed.

The appropriate register settings for a given data rate with or without CAN FD/CAN XL FAST mode tolerance are illustrated in <u>Figure 17</u>. The partial networking and CAN configuration register includes the PNCOK bit. Before setting this bit to 1, all other PN registers should have been initialized. After setting PNCOK = 1 and CPNC = 1 (in the same register), the device is initialized to use the current contents of the PN registers for wake-up by WUF. However, the CWE bit in the system interrupt enable register must also be set to 1 for general CAN bus wake-up capability.

# AN14388

### TJA1445, TJA1465 application note

# 4.2 Example SPI sequence for PN configuration and transition to Sleep mode

| Action                                         | Register name                                                        | Address                 | Content                    | Single-register<br>SPI code | Multi-register SPI<br>code         |  |

|------------------------------------------------|----------------------------------------------------------------------|-------------------------|----------------------------|-----------------------------|------------------------------------|--|

| Enable CAN as wake<br>source (CWE = 1)         | System interrupt enable register                                     | 0x010                   | 0x40                       | 0x01 01 40                  | 0x01 01 40                         |  |

| Select 11-bit format plus<br>DLC = 3           | Partial networking frame control register                            | 0x030                   | 0x43                       | 0x03 00 43                  |                                    |  |

| Set data rate = 500 kbit/s<br>and ISO filter 2 | Partial networking<br>data rate and filter<br>configuration register | 0x031                   | 0x24                       | 0x03 11 24                  | 0x03 03 43 24                      |  |

|                                                | Partial networking ID register 0                                     | 0x020                   | 0x00                       | 0x02 01 00                  |                                    |  |

| Set WUF ID                                     | Partial networking ID register 1                                     | 0x021                   | 0x00                       | 0x02 10 00                  | 0x02 07 00 00 80 0B                |  |

|                                                | Partial networking ID register 2                                     | 0x022                   | 0x80                       | 0x02 20 80                  | 1                                  |  |

| AN14388                                        | All information provid                                               | led in this document is | subject to legal disclaime | rs.                         | © 2024 NXP B.V. All rights reserve |  |

Table 6. Example SPI sequence for PN configuration and transition to Sleep mode

It is assumed that the device is Normal, Standby or ListenOnly mode, when starting the SPI sequence.

| Action                                                                   | Register name                                           | Address | Content | Single-register<br>SPI code | Multi-register SPI<br>code |  |

|--------------------------------------------------------------------------|---------------------------------------------------------|---------|---------|-----------------------------|----------------------------|--|

|                                                                          | Partial networking ID register 3                        | 0x023   | 0x0B    | 0x02 31 0B                  |                            |  |

|                                                                          | Partial networking ID<br>mask register 0                | 0x024   | 0x00    | 0x02 40 00                  |                            |  |

| Set WUF ID mask                                                          | Partial networking ID<br>mask register 1                | 0x025   | 0x00    | 0x02 51 00                  | -0x02 46 00 00 1C 04       |  |

| oct wor 1D mask                                                          | Partial networking ID<br>mask register 2                | 0x026   | 0x1C    | 0x02 61 1C                  |                            |  |

|                                                                          | Partial networking ID mask register 3                   | 0x027   | 0x04    | 0x02 70 04                  |                            |  |

|                                                                          | Partial networking data mask register 0                 | 0x028   | 0x00    | 0x02 80 00                  |                            |  |

| Set data mask 0-3                                                        | Partial networking data mask register 1                 | 0x029   | 0x00    | 0x02 91 00                  | -0x02 86 00 00 00 00       |  |

| Set data mask 0-5                                                        | Partial networking data mask register 2                 | 0x02A   | 0x00    | 0x02 A1 00                  | -                          |  |

|                                                                          | Partial networking data mask register 3                 | 0x02B   | 0x00    | 0x02 B0 00                  |                            |  |

|                                                                          | Partial networking data mask register 4                 | 0x02C   | 0x00    | 0x02 C1 00                  |                            |  |

| Set data mask 4-7                                                        | Partial networking data mask register 5                 | 0x02D   | 0xA0    | 0x02 D0 A0                  | -0x02 C7 00 A0 00 04       |  |

| Set data mask 4-7                                                        | Partial networking data mask register 6                 | 0x02E   | 0x00    | 0x02 E0 00                  |                            |  |

|                                                                          | Partial networking data mask register 7                 | 0x02F   | 0x04    | 0x02 F1 04                  | _                          |  |

| Finalize PN configuration<br>with CAN FD passive,<br>without CAN XL FAST | Partial networking and<br>CAN configuration<br>register | 0x032   | 0x07    | 0x03 21 07                  | 0x03 21 07                 |  |

|                                                                          | System interrupt status<br>register                     | 0x060   | 0xFF    | 0x06 00 FF                  |                            |  |

| Clear all interrunta                                                     | CAN interrupt status<br>register                        | 0x061   | 0xFF    | 0x06 11 FF                  |                            |  |

| Clear all interrupts                                                     | Partial networking interrupt status register            | 0x062   | 0xFF    | 0x06 21 FF                  | -0x06 06 FF FF FF FF       |  |

|                                                                          | GPIO interrupt status register <sup>[1]</sup>           | 0x063   | 0xFF    | 0x06 30 FF                  | -                          |  |

| Select Sleep mode                                                        | Mode control register                                   | 0x000   | 0x01    | 0x00 00 01                  | 0x00 00 01                 |  |

| Confirm Sleep mode (see <u>Section 3.8.1</u> )                           | Mode status register                                    | 0x070   | 0x00    | 0x07 08 00                  | 0x07 08 00                 |  |

Table 6. Example SPI sequence for PN configuration and transition to Sleep mode...continued

It is assumed that the device is Normal, Standby or ListenOnly mode, when starting the SPI sequence.

[1] This register is not available in the TJA1445A or TJA1465A. Writing to this register can be skipped. Writing is allowed but will be ignored.

AN14388 Application note

### 4.3 Software development, MCU flash memory programming

### 4.3.1 Handling of the INH signal

In an application where the INH pin controls the voltage regulator(s) directly (i.e. INH off means regulator off), the `debug jumper' (<u>Section 2.1.4</u>) may need to be set. This ensures that the voltage regulator remains active even when the transceiver enters Sleep mode due to missing in-time SPI interaction since power up or since the last wake-up from Sleep mode (<u>Section 3.5</u>).

### 4.3.2 Using a generic boot loader

A generic MCU boot loader would not be able to control the transceiver appropriately via SPI. However, the transceiver includes the Start-to-Normal Mode (SNM) feature that allows the device to boot up without SPI interaction. When the transceiver is powered up while the CAN bus is steadily dominant, it starts up automatically in Normal mode (SNM). A generic boot loader can then be used to load data via the CAN transceiver. No SPI interaction is needed. In turn, when Flash programming has been completed and the application software starts running, device modes can be controlled as normal.

SNM mode is activated automatically if the CAN bus switches to a dominant state ( $V_{CANH} - V_{CANL} > 1.1 V$ ) before the main state machine FSM\_MAIN enters Check\_SNM mode, with the dominant state maintained for at least  $t_{t(snm)}$ . This can be achieved, for example, by connecting CANL to module GND and CANH to  $V_{BAT}$  or to an auxiliary power supply > 1.5 V, before  $V_{BAT}$  powers up. CANH and CANL can be released as soon as the device has turned on INH. Note that this causes the device start-up time, from VBAT ramp-up to INH rising edge, to be lengthened by  $t_{t(snm)}$ .

The maximum voltage that may be applied to CANH is determined by the max voltage rating of the pin and by the max current or power rating of the bus termination resistors.

### 4.4 Pin failure mode and effects analysis (FMEA) of the TJA1445x/TJA1446x/ TJA1465x/TJA1466x family

| A | damage to device; bus may be affected                                                       |

|---|---------------------------------------------------------------------------------------------|

| В | no damage to device; bus communication not possible                                         |

| С | no damage to device; bus communication possible; corrupted node excluded from communication |

| D | no damage to device; bus communication possible; reduced functionality of device or system  |

#### Table 7. Failure classification used in pin FMEA tables

#### Table 8. Pin FMEA of TJA1445A and TJA1465A, part 1

|        | Short to V <sub>BAT</sub> (12 V to 40 V) |            | Short t                                                                   | o V <sub>CC</sub> (5 V) | Short t                                                                                                                      | Short to V <sub>IO</sub> (1.8 V/3.3 V/5.0 V) |                                                                    |  |

|--------|------------------------------------------|------------|---------------------------------------------------------------------------|-------------------------|------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------|--------------------------------------------------------------------|--|

| Pin    |                                          | Class Mode |                                                                           | Class                   | Mode                                                                                                                         | Class                                        | Mode                                                               |  |

| 1      | TXD                                      | A          | limiting value exceeded                                                   | С                       | TXD clamped recessive;<br>potential damage to the<br>$\mu$ C I/O or the complete $\mu$ C<br>at V <sub>IO</sub> = 1.8 V-3.3 V | С                                            | TXD clamped recessive                                              |  |

| 2      | GND                                      | С          | node is left unpowered<br>and behaves passive to<br>the bus (biasing off) | С                       | V <sub>CC</sub> undervoltage<br>detected; device behaves<br>passive to the bus (biasing<br>on)                               | С                                            | V <sub>IO</sub> undervoltage detected;<br>device enters Sleep mode |  |

| 3      | VCC                                      | A          | limiting value exceeded                                                   | -                       | n/a                                                                                                                          | D                                            | potential damage to μC<br>I/O pin at 1.8 V-3.3 V                   |  |

| AN1438 | 8                                        |            | All information                                                           | n provided in this      | s document is subject to legal disclaimers.                                                                                  |                                              | © 2024 NXP B.V. All rights reserved.                               |  |

| Short |      |            | o V <sub>BAT</sub> (12 V to 40 V)                           |       | o V <sub>CC</sub> (5 V)                                                                                                                                                           | Short to V <sub>IO</sub> (1.8 V/3.3 V/5.0 V) |                                                                                                                                             |  |

|-------|------|------------|-------------------------------------------------------------|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------|--|

| Pin   |      | Class Mode |                                                             | Class | Mode                                                                                                                                                                              | Class                                        | Mode                                                                                                                                        |  |

|       |      |            |                                                             |       |                                                                                                                                                                                   |                                              | $V_{IO}$ or $V_{CC}$ undervoltage detected with device behaving passive to the bus (biasing on)                                             |  |

| 4     | RXD  | A          | limiting value exceeded                                     | С     | RXD clamped recessive;<br>bus communication may<br>be disturbed; potential<br>damage to the $\mu$ C I/O or<br>the complete $\mu$ C at V <sub>IO</sub> =<br>1.8 V-3.3 V            | С                                            | RXD clamped recessive;<br>bus communication may<br>be disturbed                                                                             |  |

| 5     | VIO  | A          | limiting value exceeded                                     | D     | host interface voltage<br>pulled to higher V <sub>CC</sub><br>supply (5 V); potential<br>damage to the $\mu$ C I/O or<br>the complete $\mu$ C at V <sub>IO</sub> =<br>1.8 V-3.3 V | -                                            | n/a                                                                                                                                         |  |

| 6     | SDO  | A          | limiting value exceeded                                     | С     | cannot read SPI from<br>device; behavior depends<br>on software; potential<br>damage to the $\mu$ C I/O or<br>the complete $\mu$ C at V <sub>IO</sub> =<br>1.8 V-3.3 V            | С                                            | cannot read SPI from<br>device; behavior depends<br>on software                                                                             |  |

| 7     | INH  | D          | INH-controlled regulators remain on permanently             | D     | INH-controlled regulators<br>may remain on<br>permanently                                                                                                                         | С                                            | INH-controlled regulators<br>may remain on or off<br>permanently                                                                            |  |

| 8     | SCK  | A          | limiting value exceeded                                     | С     | no communication towards<br>device; potential damage<br>to the $\mu$ C I/O or the<br>complete $\mu$ C at V <sub>IO</sub> =<br>1.8 V-3.3 V                                         | С                                            | no communication towards device                                                                                                             |  |

| 9     | WAKE | D          | local wake-up not possible                                  | D     | local wake-up not possible                                                                                                                                                        | D                                            | local wake-up not possible                                                                                                                  |  |

| 10    | VBAT | -          | n/a                                                         | A     | limiting value exceeded                                                                                                                                                           | A                                            | limiting value exceeded                                                                                                                     |  |

| 11    | SDI  | A          | limiting value exceeded                                     | С     | no communication towards<br>device; potential damage<br>to the $\mu$ C I/O or the<br>complete $\mu$ C at V <sub>IO</sub> =<br>1.8 V-3.3 V                                         | С                                            | no communication towards device                                                                                                             |  |

| 12    | CANL | В          | bus clamped recessive;<br>bus communication not<br>possible | В     | bus clamped recessive;<br>bus communication not<br>possible                                                                                                                       | В                                            | CANL clamped recessive;<br>bus communication might<br>be possible at low $V_{IO}$ ,<br>but in principle no bus<br>communication is possible |  |

| 13    | CANH | D          | degradation of EMC; bit timing violation possible           | D     | degradation of EMC; bit timing violation possible                                                                                                                                 | D                                            | degradation of EMC; bit timing violation possible                                                                                           |  |

| 14    | SCSN | A          | limiting value exceeded                                     | С     | no communication towards<br>device; potential damage<br>to the $\mu$ C I/O or the<br>complete $\mu$ C at V <sub>IO</sub> =<br>1.8 V-3.3 V                                         | С                                            | no communication towards device                                                                                                             |  |

### Table 8. Pin FMEA of TJA1445A and TJA1465A, part 1...continued

AN14388

|     |               | Short t          | o GND                                                                                                                       | Pin ope | en                                                                                                                                         | Short to neighbor |                                                                                                                                                                                     |  |

|-----|---------------|------------------|-----------------------------------------------------------------------------------------------------------------------------|---------|--------------------------------------------------------------------------------------------------------------------------------------------|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Pin | in Class Mode |                  | Mode                                                                                                                        | Class   | Mode                                                                                                                                       | Class             | Mode                                                                                                                                                                                |  |

| 1   | TXD           | С                | transmitter disabled (either<br>because it is not able to<br>enter CAN Active mode,<br>or due to a TXD dominant<br>timeout) | С       | TXD clamped recessive                                                                                                                      | С                 | TXD-GND: transmitter<br>disabled (either because<br>it is not able to enter CAN<br>Active mode, or due to a<br>TXD dominant timeout)                                                |  |

| 2   | GND           | -                | n/a                                                                                                                         | С       | floating voltages on the<br>supply pin can lead to<br>an undervoltage; device<br>then enters Off mode and<br>behaves passive to the<br>bus | С                 | GND-VCC: V <sub>CC</sub><br>undervoltage detected;<br>device behaves passive to<br>the bus (biasing on)                                                                             |  |

| 3   | VCC           | C                | V <sub>CC</sub> undervoltage<br>detected; device behaves<br>passive to the bus (biasing<br>on)                              | С       | V <sub>CC</sub> undervoltage<br>detected; device behaves<br>passive to the bus (biasing<br>on)                                             | C                 | VCC-RXD: RXD<br>clamped recessive; bus<br>communication may<br>be disturbed; potential<br>damage to the $\mu$ C I/O or<br>the complete $\mu$ C at V <sub>IO</sub> =<br>1.8 V-3.3 V  |  |

| 4   | RXD           | С                | RXD clamped dominant                                                                                                        | С       | when the MCU signal is<br>floating, the node may<br>continue to generate<br>error frames until it enters<br>bus-off state                  | С                 | RXD-VIO: RXD<br>clamped recessive; bus<br>communication may be<br>disturbed                                                                                                         |  |

| 5   | VIO           | С                | V <sub>IO</sub> undervoltage detected;<br>device enters Sleep mode                                                          | С       | V <sub>IO</sub> undervoltage detected;<br>device enters Sleep mode                                                                         | С                 | VIO-SDO: cannot read<br>SPI from device; behavior<br>depends on software                                                                                                            |  |

| 6   | SDO           | C                | cannot read SPI from<br>device; behavior depends<br>on software                                                             | С       | cannot read SPI from<br>device; behavior depends<br>on software                                                                            | A                 | SDO-INH: cannot read<br>SPI from device; potential<br>damage to the $\mu$ C I/O<br>or the complete $\mu$ C due<br>to INH output voltage;<br>SDO pin could also be<br>damaged        |  |

| 7   | INH           | C <sup>[1]</sup> | INH-controlled regulators remain off permanently                                                                            | С       | INH-controlled regulators remain off permanently                                                                                           | -                 | n/a                                                                                                                                                                                 |  |

| 8   | SCK           | С                | no communication towards<br>device                                                                                          | C       | no communication towards<br>device                                                                                                         | A                 | SCK-WAKE: potential damage to SCK pin if WAKE pin voltage related to $V_{BAT}$ supply; potential damage to the $\mu$ C I/O or the complete $\mu$ C; no communication towards device |  |

| 9   | WAKE          | D                | local wake-up not possible                                                                                                  | D       | local wake-up not possible                                                                                                                 | D                 | WAKE-VBAT: local wake-<br>up not possible                                                                                                                                           |  |

| 10  | VBAT          | С                | node left unpowered and<br>behaves passive to the<br>bus (biasing off)                                                      | С       | node left unpowered and<br>behaves passive to the<br>bus (biasing off)                                                                     | A                 | VBAT-SDI: SDI limiting value exceeded; potential damage to the $\mu$ C I/O or the complete $\mu$ C                                                                                  |  |

### Table 9. Pin FMEA of TJA1445A and TJA1465A, part 2

AN14388 Application note

|     |      | Short t | o GND                                                       | Pin ope    | en                                 | Short t | o neighbor                                                                                                                                  |