# AN14356

# NX48P0407 application note Rev. 1.0 — 26 August 2024

**Application note**

#### **Document information**

| Information | Content                                                                                                                                                                          |

|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Keywords    | NX48P0407, USB Type C, CC1/2 and SBU1/2 Protection                                                                                                                               |

| Abstract    | The NX48P0407 is a CC and SBU protection IC, which can protect the short-to-VBUS damage on CC and SBU pins of Type-C by ultra-fast response of overvoltage protection detection. |

NX48P0407 application note

## 1 Scope and setup of the application note

#### 1.1 Scope

This application note discusses the NX48P0407 functions for general applications and the notes when testing this device.

#### 1.2 General setup of the application note

The setup of this document is made in such a way, that a chapter or paragraph on a selected subject can be read as a stand-alone explanation with a minimum of cross-references to other document parts or the datasheet. This will lead to some repetition of information with in the application note and to descriptions or figures that are similar to the ones published in the NX48P0407 datasheet. In most cases typical values are given to enhance the readability.

- · Chapter 2: Introduction and features

- Chapter 3: IC pin overview with a summary of the functions

- · Chapter 4: Application diagram

- Chapter 5: System description

- Chapter 6: Debugging an application circuit

- · Chapter 7: optional circuits and application tricks

- · Chapter 8: PCB design and layout guidelines

#### 1.3 Related documents and tools

More documents and design tools can be found at the product page of NX48P0407 or through the local sales office.

NX48P0407 application note

#### 2 Introduction

#### 2.1 Introduction

NX48P0407 is a single chip USB-Type C port protection solution. CC1/CC2 and SBU1/SBU2 pins in the system side are protected from 48 V short to VBUS, which are located next to the VBUS pins.

#### 2.2 Features

The NX48P0407 is a CC and SBU protection IC which can protect the short-to-VBUS damage on CC and SBU pins of Type-C by ultra-fast response of over voltage protection detection. USB Type-C allows VBUS voltage to increase up to 48 V through PD 3.1 protocol. CC1/2 and SBU1/2 pins can be shorted to VBUS of 48 V due to mechanical twisting and sliding of the connector since Type-C connector contact pins are 25% closer to each other than a micro USB connector. Moisture or fine dust may also cause the 48 V VBUS pin to be shorted to adjacent pins.

The NX48P0407 integrates IEC 61000-4-2 ESD protection on CON\_CC1 and CON\_CC2,+/-15 kV air discharge and +/-8 kV contact discharge, which helps to reduce external BOM cost. NX48P0407 CON\_CC1/2 and CON\_SBU1/2 pins are designed to be protected from surges up to +80 V.

#### 2.2.1 Key features

- Type-C 48 V short-to-VBUS protection

- CON\_CC1/CON\_CC2: up to 60 V<sub>DC</sub>

- CON SBU1/CON SBU2: up to 60 VDC

- Dead-battery mode Rd integrated on CON CCx

- Low RON for OVP FET paths

- CC OVP Switch: 250 mΩ

- SBU OVP Switch: 3.6 Ω

Robust IEC-61000-4-2 ESD protection

- Contact discharge +/-8 kV: CON CCx/CON SBUx

- Air discharge +/-15 kV: CON\_CCx/CON\_SBUx

- Low standby quiescent current of CC path: ~40 μA

- · Fast OVP turn off time: 60 ns

- HVQFN16 package

- USB-PD EPR application

- · Laptop, notebook, computing PC

NX48P0407 application note

## 3 Pinning information

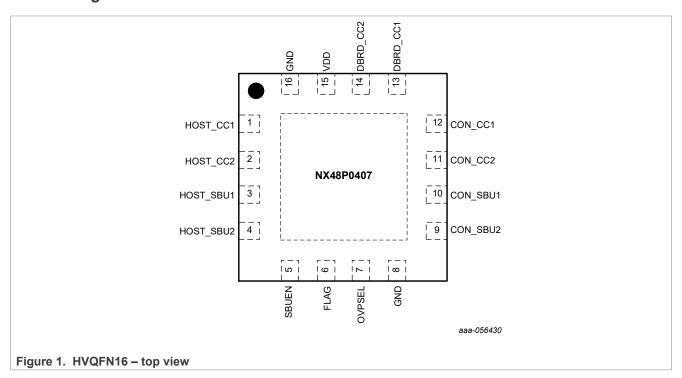

#### 3.1 Pinning

## 3.2 Pin description

Table 1. Pin type definition

| Pin type | Description        | Pin type | Description         | Pin type | Description           |

|----------|--------------------|----------|---------------------|----------|-----------------------|

| PI       | Power Input        | AO       | Analog Output       | DIO      | Digital Input/ Output |

| РО       | Power output       | AIO      | Analog Input/Output | AG       | Analog Ground         |

| PIO      | Power Input/Output | DI       | Digital Input       | PG       | Power Ground          |

| Al       | Analog Input       | DO       | Digital Output      |          |                       |

Table 2. Pin description

| Pin name  | Pin<br>number | Туре  | Description                                                                                                                    |

|-----------|---------------|-------|--------------------------------------------------------------------------------------------------------------------------------|

| HOST_CC1  | 1             | P/AIO | System side CC1. Connect CC1 of USB CC/PD controller.                                                                          |

| HOST_CC2  | 2             | P/AIO | System side CC2. Connect CC2 of USB CC/PD controller.                                                                          |

| HOST_SBU1 | 3             | A/DIO | System side SBU1.                                                                                                              |

| HOST_SBU2 | 4             | A/DIO | System side SBU2.                                                                                                              |

| SBUEN     | 5             | DI    | SBU switch enable/disable control pin. SBUEN is driven HIGH to enable SBU switch. (1.8 M $\Omega$ Internal pull-down resistor) |

Table 2. Pin description...continued

| Pin name | Pin<br>number | Туре  | Description                                                                                                            |

|----------|---------------|-------|------------------------------------------------------------------------------------------------------------------------|

| FLAG     | 6             | DO    | Open-drain output indicating fault condition. Low when Fault condition happens, external pull-up resistor is required. |

| OVPSEL   | 7             | DI    | For SBU OVP SEL of options                                                                                             |

| GND      | 8             | AG    | Ground                                                                                                                 |

| CON_SBU2 | 9             | A/DIO | Type-C connector side SBU2. Connect SBU2 of Type-C USB connector.                                                      |

| CON_SBU1 | 10            | A/DIO | Type-C connector side SBU1. Connect SBU2 of Type-C USB connector.                                                      |

| CON_CC2  | 11            | P/AIO | Type-C connector side CC2. Connect CC2 of Type-C USB connector.                                                        |

| CON_CC1  | 12            | P/AIO | Type-C connector side CC1. Connect CC2 of Type-C USB connector.                                                        |

| DBRD_CC1 | 13            | AG    | Dead-Battery Mode RD of CC1.                                                                                           |

| DBRD_CC2 | 14            | AG    | Dead-Battery Mode RD of CC2.                                                                                           |

| VDD      | 15            | PI    | Power supply input; connect System voltage and bypass 1µF capacitor to GND.                                            |

| GND      | 16            | AG    | Ground.                                                                                                                |

NX48P0407 application note

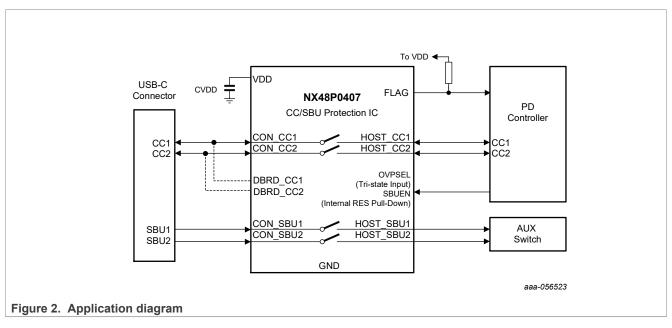

## 4 Application diagram

NX48P0407 is placed in front of Type-C connector and protects CC and SBU pins in System side from 48 V VBUS short, ESD and surge.

NX48P0407 has DBRD circuit on both CON\_CC1 and CON\_CC2 when VDD is below UVLO threshold, i.e., dead battery condition. It allows Type-C adapter to detect sink through CC and start providing 5 V VBUS. Main charger regulates system voltage from the VBUS. Once VDD comes up, NX48P0407 enables switches and disconnects the DBRD circuit from CON\_CC1 and CON\_CC2.

NX48P0407 application note

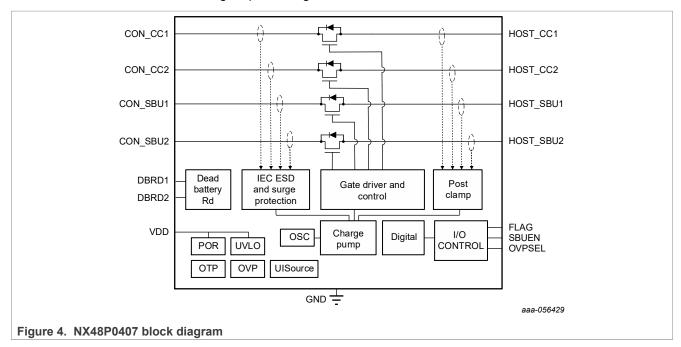

### 5 System description

#### 5.1 Power state table

When VDD is below VDDUVLO, NX48P0407 stays in shutdown mode. Bias circuit, switches and all comparators are disabled, but Rd clamp circuits on CON\_CC1 and CON\_CC2 are enabled. It allows the Type-C adapter to detect Rd and to supply 5 V through VBUS pin in dead battery condition.

NX48P0407 enters standby mode when VDD exceeds VDDUVLO. CC switch automatically turns on and SBU switch is controlled by SBUEN. After CC switch is fully turned ON, the Rd clamp circuit is disabled. 5 V VCONN power supply on HOST\_CC1 or \_HOST\_CC2 should be supplied after VDD is valid.

Table 3. Power states

| Power states         | VDD       | FLAG | SBUEN | Dead Battery-<br>Rd | CC Switch | SBU Switch |

|----------------------|-----------|------|-------|---------------------|-----------|------------|

| Dead-Battery<br>Mode | < VDDUVLO | Hi-Z | X     | ON                  | OFF       | OFF        |

| Power ON_CC          | > VDDUVLO | Hi-Z | Low   | OFF                 | ON        | OFF        |

| Power ON_CC/<br>SBU  | > VDDUVLO | Hi-Z | High  | OFF                 | ON        | ON         |

#### 5.2 Protection

#### 5.2.1 Overvoltage protection

NX48P0407 has short circuit protection of CON\_CC1/2 and CON\_SBU1/2 when they are shorted by 48 V. CC switch overvoltage threshold is  $V_{OVP\_CC}$  to guarantee VCONN power supply passes to VCONN load, which is maximum 5.5 V by USB Type-C spec. SBU switch overvoltage threshold is  $V_{OVP\_SBU}$  to securely turn the switch off and prevent high voltage to SBU in system side.

Once overvoltage on any channel is detected, the switch is quickly turned off within  $t_{OVP\_RES}$ , to prevent overvoltage to system side. FLAG pin goes LOW in  $t_{FLAG\_RES}$  to inform system of the fault condition. If the voltage of the channel triggered OVP comes down below overvoltage threshold for  $t_{OVP\_DEB}$ , the switch is turned back on and FLAG pin gets Hi-Z. Refer to Figure 5.

Each of the four switches for CC1/2 and SBU1/2 has its own OVP comparator and is controlled by its comparator independently. If CC1 voltage exceeds OVP threshold, the CC1 switch is turned off, but the other switches stay ON.

#### 5.2.2 Post-clamping protection

NX48P0407 has a post-clamping protection to clamp extra voltage on HOST\_CC1/CC2, HOST\_SBU1/SBU2 in system side. When shorting with VBUS, the voltage on CON\_CCx and SBU\_CCx is rapidly increased. Even though NX48P0407 features ultra-fast response time for overvoltage condition, the overvoltage may pass through to HOST\_CCx / HOST\_SBUx during the response time,  $t_{OVP\_RES}$ . NX48P0407 post-clamping circuit provides secondary protection to clamp the voltage on HOST\_CCx and HOST\_SBUx in system side, to prevent exceeding 7V in HOST\_CCx and 7 V or 4.5 V in HOST\_SBUx by OVPSEL settings.

#### 5.2.3 Undervoltage protection

When VDD voltage exceeds UVLO threshold, NX48P0407 behaves in normal, dead-battery mode. Rd will be removed with a delay time after CC OVP switch turns on. Otherwise, NX48P0407 will be operating in dead-battery mode and present dead-battery mode Rd on CON\_CC1 and CON\_CC2 pin.

AN14356

NX48P0407 application note

#### 5.2.4 Overtemperature protection

When NX48P0407 operates in normal power on mode, OTP detection circuit is active for monitoring if device temperature exceeds 140 °C. Once OTP occurs, the CC OVP switch will always turn on while FLAG will be asserted to Low and it turns to Hi-Z until temperature goes back to 120 °C.

#### 5.2.5 IEC-61000-4-2 contact ESD protection

NX48P0407 integrates IEC-61000-4-2 ESDs on CON\_CCx and CON\_SBUx up to contact +/-8 kV in CC channels and +/- 8 kV in SBU channels as well, and Air +/- 15 kV to help to reduce the external BOM in USB-C CC/SBU signal path design.

#### 5.2.6 IEC-61000-4-5 surge protection

NX48P0407 integrates IEC-61000-4-5 TVSs on CON\_CCx and CON\_SBUx up to +80 V to help to reduce the external BOM in USB-C CC/SBU signal path design.

NX48P0407 application note

## 6 Debugging an application circuit

#### 6.1 FLAG Function

#### 6.1.1 FLAG signal

FLAG pin is open-drain configuration. When there is no any protection event like OVP or OTP, it behaves as Hi-Z state. If FLAG is not used in system, leave it floating or connected to GND. When OVP or OTP occurs, FLAG asserts "LOW" state after the delay of t<sub>FLAG RES</sub>.

#### 6.1.2 FLAG and switch condition during protections

NX48P0407 performs different kinds of behavior during OTP and OVP in CC or SBU channel. Please refer to Table 4 for the operation.

Table 4. NX48P0407 protection condition and behaviors of FLAG and switch configuration

| Protection              | Condition              | SBUEN | FLAG | CC OVP switch | SBU OVP switch |

|-------------------------|------------------------|-------|------|---------------|----------------|

| Overtemperature         | Tj > TOTP              | LOW   | LOW  | ON            | OFF            |

| Overtemperature         | Tj > TOTP              | HIGH  | LOW  | ON            | ON             |

| Overvoltage on CON_CCx  | VCON_CCX > VOVPCC      | LOW   | LOW  | OFF           | OFF            |

| Overvoltage on CON_CCx  | VCON_CCX > VOVPCC      | HIGH  | LOW  | OFF           | ON             |

| Overvoltage on CON_SBUx | VCON_SBUX > VOVPSBU    | LOW   | Hi-Z | ON            | OFF            |

| Overvoltage on CON_SBUx | VCON_SBUX ><br>VOVPSBU | HIGH  | LOW  | ON            | OFF            |

#### 6.2 SBUEN function

When SBUEN=High, SBU OVP path is turned on, otherwise, the path is OFF. SBUEN has internal pull down of 1.8 M $\Omega$ . SBUEN is also capable of 1.2/1.8/3.3 V control signal by PD Controller, MCU or other CPUs.

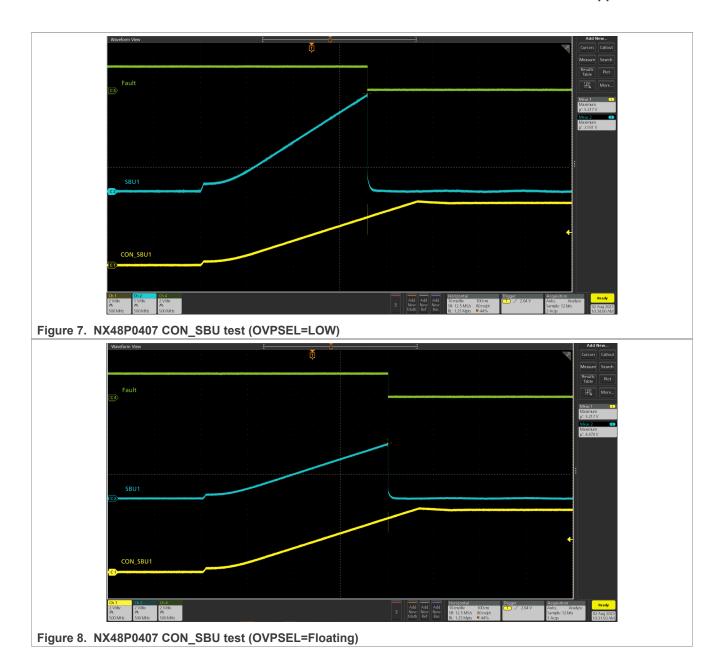

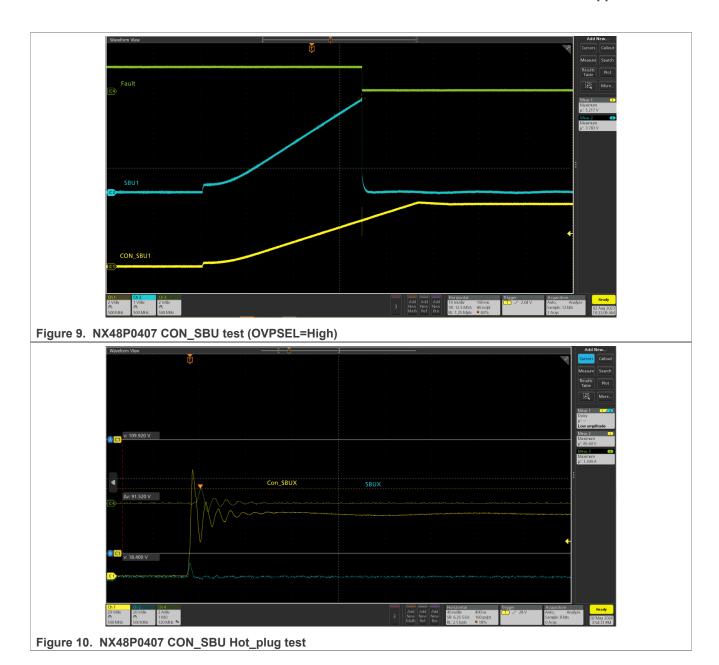

#### 6.3 OVPSEL function

NX48P0407 can reverse several OVP thresholds of SBU path for different kinds of signaling. Please refer to Table 5.

Table 5. NX48P0407 protection condition and behaviors of FLAG and switch configuration

| Symbol   | Parameter                 | Conditions                                            | Min  | Тур  | Max  | Unit |

|----------|---------------------------|-------------------------------------------------------|------|------|------|------|

|          |                           | SBU OVP Switch                                        |      |      |      |      |

| VOVP_SBU | OVP Threshold on CON_SBUx | VDD = 3.3 V, VCON_SBUx rising, SBUEN=High, OVPSEL=VDD | 3.50 | 3.65 | 3.80 | V    |

|          |                           | VDD = 3.3 V, VCON_SBUx rising, SBUEN=High, OVPSEL=GND | 3.65 | 3.85 | 4.05 | V    |

AN14356

All information provided in this document is subject to legal disclaimers.

© 2024 NXP B.V. All rights reserved.

Document feedback

Table 5. NX48P0407 protection condition and behaviors of FLAG and switch configuration...continued

| Symbol           | Parameter                       | Conditions                                                                                                                           | Min  | Тур  | Max  | Unit |

|------------------|---------------------------------|--------------------------------------------------------------------------------------------------------------------------------------|------|------|------|------|

|                  |                                 | VDD = 3.3 V, VCON_SBUx rising, SBUEN=High, OVPSEL=floating                                                                           | 4.15 | 4.35 | 4.55 | V    |

| VCLAMP_HOST_SBUx | Clamp voltage<br>on system side | Hot plug voltage on CON_SBUx =48 V with load of 150nF cap and 40 Ω in series to GND on HOST_SBUx with 40 V/us, for OVPSEL=Floating   |      | 7    |      | V    |

|                  |                                 | Hot plug voltage on CON_SBUx =48 V with load of 150nF cap and 40 Ω in series to GND on HOST_SBUx with 40 V/us, for OVPSEL=VDD or GND |      | 4.5  |      | V    |

NX48P0407 application note

## 7 Optional circuit and application tricks

#### 7.1 Overvoltage protection

NX48P0407 has short circuit protection of CON\_CC1/2 and CON\_SBU1/2 up to 48 V. CC switch overvoltage threshold is maximum 6 V. SBU switch overvoltage threshold determined of OVPSEL setting.

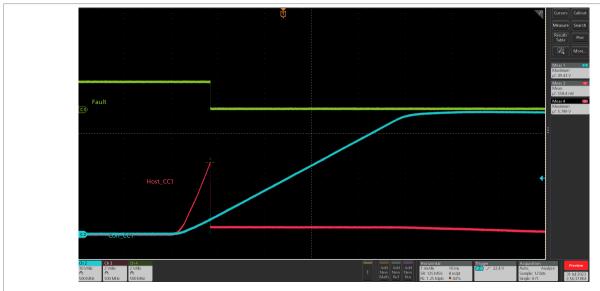

Figure 5. NX48P0407 CON\_CC OVP test

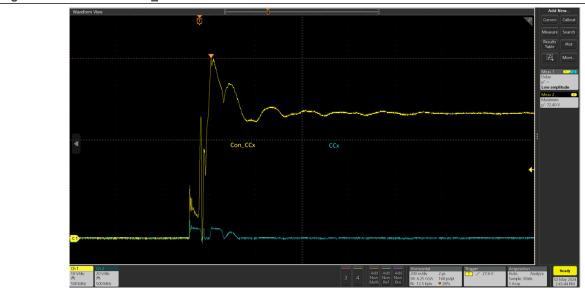

Figure 6. NX48P0407 CON\_CC Hot\_plug test

NX48P0407 application note

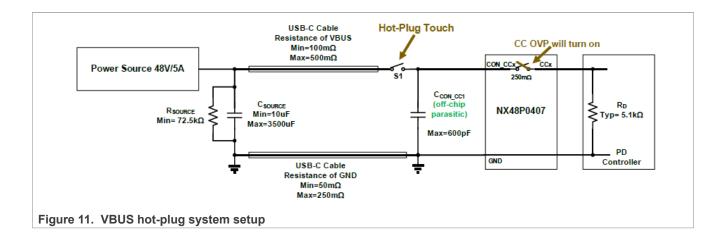

#### 7.2 Hot-plug protection of 48 V touch

NX48P0407 can pass the 48 V hot-plug testing, with the system parameters of hot-plug condition below:

- Source capacitance from 10 μF to 3500 μF

- Source resistance to GND with minimum of 72.5 k $\Omega$ .

- USB-C resistance of VBUS path from 100 m $\Omega$  to 500 m $\Omega$ .

- USB-C resistance of GND path from 50 m $\Omega$  to 250 m $\Omega$ ,

- CON\_CCx capacitance for USB-PD Spec from 0 pF to 600 pF

NX48P0407 application note

## PCB design and layout guidelines

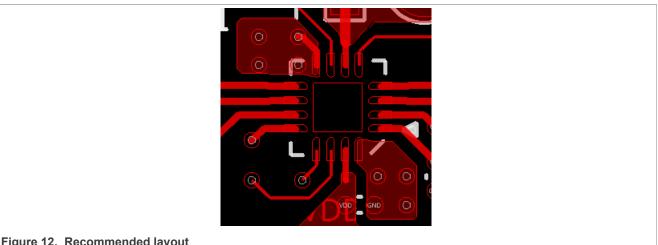

#### 8.1 Recommend capacitances

- 1. The capacitances of VDD should be as close as possible to NX48P0407.

- 2. The recommended capacitance value for VDD is 1  $\mu$ F.

#### 8.2 Recommend layout guide for no HDI PCB

Figure 12. Recommended layout

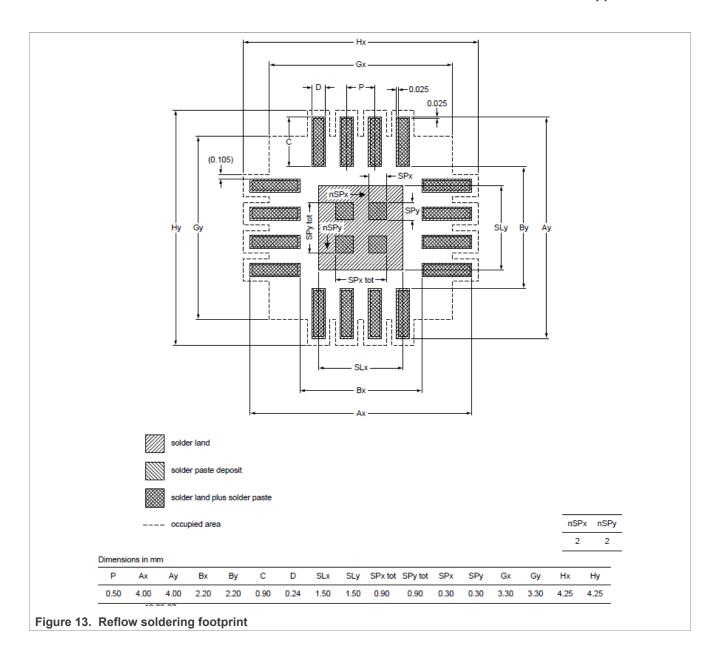

#### 8.3 Soldering

Footprint information for reflow soldering

NX48P0407 application note

## 9 Revision history

#### Table 6. Revision history

| Document ID   | Release date   | Description     |

|---------------|----------------|-----------------|

| AN14356 v.1.0 | 26 August 2024 | Initial version |

#### NX48P0407 application note

## **Legal information**

#### **Definitions**

**Draft** — A draft status on a document indicates that the content is still under internal review and subject to formal approval, which may result in modifications or additions. NXP Semiconductors does not give any representations or warranties as to the accuracy or completeness of information included in a draft version of a document and shall have no liability for the consequences of use of such information.

#### **Disclaimers**

Limited warranty and liability — Information in this document is believed to be accurate and reliable. However, NXP Semiconductors does not give any representations or warranties, expressed or implied, as to the accuracy or completeness of such information and shall have no liability for the consequences of use of such information. NXP Semiconductors takes no responsibility for the content in this document if provided by an information source outside of NXP Semiconductors.

In no event shall NXP Semiconductors be liable for any indirect, incidental, punitive, special or consequential damages (including - without limitation - lost profits, lost savings, business interruption, costs related to the removal or replacement of any products or rework charges) whether or not such damages are based on tort (including negligence), warranty, breach of contract or any other legal theory.

Notwithstanding any damages that customer might incur for any reason whatsoever, NXP Semiconductors' aggregate and cumulative liability towards customer for the products described herein shall be limited in accordance with the Terms and conditions of commercial sale of NXP Semiconductors.

Right to make changes — NXP Semiconductors reserves the right to make changes to information published in this document, including without limitation specifications and product descriptions, at any time and without notice. This document supersedes and replaces all information supplied prior to the publication hereof.

Suitability for use — NXP Semiconductors products are not designed, authorized or warranted to be suitable for use in life support, life-critical or safety-critical systems or equipment, nor in applications where failure or malfunction of an NXP Semiconductors product can reasonably be expected to result in personal injury, death or severe property or environmental damage. NXP Semiconductors and its suppliers accept no liability for inclusion and/or use of NXP Semiconductors products in such equipment or applications and therefore such inclusion and/or use is at the customer's own risk

**Applications** — Applications that are described herein for any of these products are for illustrative purposes only. NXP Semiconductors makes no representation or warranty that such applications will be suitable for the specified use without further testing or modification.

Customers are responsible for the design and operation of their applications and products using NXP Semiconductors products, and NXP Semiconductors accepts no liability for any assistance with applications or customer product design. It is customer's sole responsibility to determine whether the NXP Semiconductors product is suitable and fit for the customer's applications and products planned, as well as for the planned application and use of customer's third party customer(s). Customers should provide appropriate design and operating safeguards to minimize the risks associated with their applications and products.

NXP Semiconductors does not accept any liability related to any default, damage, costs or problem which is based on any weakness or default in the customer's applications or products, or the application or use by customer's third party customer(s). Customer is responsible for doing all necessary testing for the customer's applications and products using NXP Semiconductors products in order to avoid a default of the applications and the products or of the application or use by customer's third party customer(s). NXP does not accept any liability in this respect.

Terms and conditions of commercial sale — NXP Semiconductors products are sold subject to the general terms and conditions of commercial sale, as published at https://www.nxp.com/profile/terms, unless otherwise agreed in a valid written individual agreement. In case an individual agreement is concluded only the terms and conditions of the respective agreement shall apply. NXP Semiconductors hereby expressly objects to applying the customer's general terms and conditions with regard to the purchase of NXP Semiconductors products by customer.

**Export control** — This document as well as the item(s) described herein may be subject to export control regulations. Export might require a prior authorization from competent authorities.

Suitability for use in non-automotive qualified products — Unless this document expressly states that this specific NXP Semiconductors product is automotive qualified, the product is not suitable for automotive use. It is neither qualified nor tested in accordance with automotive testing or application requirements. NXP Semiconductors accepts no liability for inclusion and/or use of non-automotive qualified products in automotive equipment or applications.

In the event that customer uses the product for design-in and use in automotive applications to automotive specifications and standards, customer (a) shall use the product without NXP Semiconductors' warranty of the product for such automotive applications, use and specifications, and (b) whenever customer uses the product for automotive applications beyond NXP Semiconductors' specifications such use shall be solely at customer's own risk, and (c) customer fully indemnifies NXP Semiconductors for any liability, damages or failed product claims resulting from customer design and use of the product for automotive applications beyond NXP Semiconductors' standard warranty and NXP Semiconductors' product specifications.

**HTML publications** — An HTML version, if available, of this document is provided as a courtesy. Definitive information is contained in the applicable document in PDF format. If there is a discrepancy between the HTML document and the PDF document, the PDF document has priority.

**Translations** — A non-English (translated) version of a document, including the legal information in that document, is for reference only. The English version shall prevail in case of any discrepancy between the translated and English versions.

Security — Customer understands that all NXP products may be subject to unidentified vulnerabilities or may support established security standards or specifications with known limitations. Customer is responsible for the design and operation of its applications and products throughout their lifecycles to reduce the effect of these vulnerabilities on customer's applications and products. Customer's responsibility also extends to other open and/or proprietary technologies supported by NXP products for use in customer's applications. NXP accepts no liability for any vulnerability. Customer should regularly check security updates from NXP and follow up appropriately. Customer shall select products with security features that best meet rules, regulations, and standards of the intended application and make the ultimate design decisions regarding its products and is solely responsible for compliance with all legal, regulatory, and security related requirements concerning its products, regardless of any information or support that may be provided by NXP.

NXP has a Product Security Incident Response Team (PSIRT) (reachable at <a href="PSIRT@nxp.com">PSIRT@nxp.com</a>) that manages the investigation, reporting, and solution release to security vulnerabilities of NXP products.

**NXP B.V.** — NXP B.V. is not an operating company and it does not distribute or sell products.

#### **Trademarks**

Notice: All referenced brands, product names, service names, and trademarks are the property of their respective owners.

NXP — wordmark and logo are trademarks of NXP B.V.

AN14356

## NX48P0407 application note

## **Tables**

|         | Pin type definition                |         | •                            |    |

|---------|------------------------------------|---------|------------------------------|----|

| iab. Z. | Pin description4                   |         | behaviors of FLAG and switch |    |

| Tab. 3. | Power states 8                     |         | configuration                | 10 |

| Tab. 4. | NX48P0407 protection condition and | Tab. 6. | Revision history             | 18 |

|         | behaviors of FLAG and switch       |         |                              |    |

|         | configuration 10                   |         |                              |    |

## NX48P0407 application note

## **Figures**

| Fig. 1. | HVQFN16 – top view4              | Fig. 8.  | NX48P0407 CON_SBU test          |    |

|---------|----------------------------------|----------|---------------------------------|----|

| Fig. 2. | Application diagram6             |          | (OVPSEL=Floating)               | 13 |

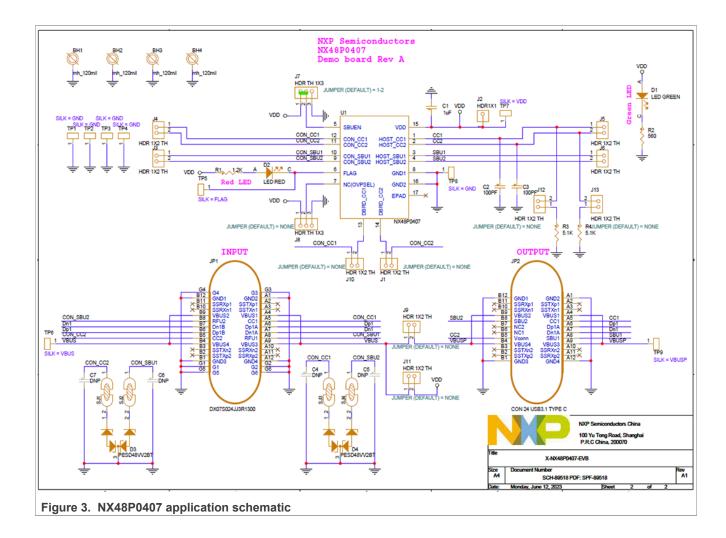

| Fig. 3. | NX48P0407 application schematic7 | Fig. 9.  | NX48P0407 CON_SBU test          |    |

| Fig. 4. | NX48P0407 block diagram9         | _        | (OVPSEL=High)                   | 14 |

| Fig. 5. | NX48P0407 CON CC OVP test 12     | Fig. 10. | NX48P0407 CON_SBU Hot_plug test | 14 |

| Fig. 6. | NX48P0407 CON CC Hot plug test12 |          | VBUS hot-plug system setup      |    |

| Fig. 7. | NX48P0407 CON SBU test           | Fig. 12. | Recommended layout              | 16 |

| Ū       | (OVPSEL=LOW)13                   | Fig. 13. | Reflow soldering footprint      | 17 |

#### NX48P0407 application note

#### **Contents**

| 1     | Scope and setup of the application note | 2  |

|-------|-----------------------------------------|----|

| 1.1   | Scope                                   | 2  |

| 1.2   | General setup of the application note   | 2  |

| 1.3   | Related documents and tools             | 2  |

| 2     | Introduction                            | 3  |

| 2.1   | Introduction                            | 3  |

| 2.2   | Features                                | 3  |

| 2.2.1 | Key features                            | 3  |

| 3     | Pinning information                     | 4  |

| 3.1   | Pinning                                 | 4  |

| 3.2   | Pin description                         | 4  |

| 4     | Application diagram                     | 6  |

| 5     | System description                      | 8  |

| 5.1   | Power state table                       | 8  |

| 5.2   | Protection                              |    |

| 5.2.1 | Overvoltage protection                  | 8  |

| 5.2.2 | Post-clamping protection                | 8  |

| 5.2.3 | Undervoltage protection                 | 8  |

| 5.2.4 | Overtemperature protection              |    |

| 5.2.5 | IEC-61000-4-2 contact ESD protection    |    |

| 5.2.6 | IEC-61000-4-5 surge protection          | 9  |

| 6     | Debugging an application circuit        | 10 |

| 6.1   | FLAG Function                           | 10 |

| 6.1.1 | FLAG signal                             | 10 |

| 6.1.2 | FLAG and switch condition during        |    |

|       | protections                             | 10 |

| 6.2   | SBUEN function                          | 10 |

| 6.3   | OVPSEL function                         |    |

| 7     | Optional circuit and application tricks | 12 |

| 7.1   | Overvoltage protection                  |    |

| 7.2   | Hot-plug protection of 48 V touch       |    |

| 8     | PCB design and layout guidelines        | 16 |

| 8.1   | Recommend capacitances                  | 16 |

| 8.2   | Recommend layout guide for no HDI PCB   | 16 |

| 8.3   | Soldering                               | 16 |

| 9     | Revision history                        | 18 |

|       | Legal information                       | 19 |

Please be aware that important notices concerning this document and the product(s) described herein, have been included in section 'Legal information'.