# AN14317 Low power implementation on MCXN236 Rev. 1.0 — 14 May 2024

**Application note**

#### **Document information**

| Information | Content                                                                                                                                                                                                                                                   |

|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Keywords    | AN14317, MCXN23x, Low power, Power consumption, Wake-up time                                                                                                                                                                                              |

| Abstract    | This application note introduces the power domains, power modes, low power entry, wake-up, and low power and wake-up optimization of MCXN23x. It also provides a demo to reproduce the typical power consumption and wake-up time data in the data sheet. |

# 1 Introduction

The MCX N23x series microcontrollers combine the Arm Cortex-M33 TrustZone core with multiple high-speed connectivity options running at 150 MHz, providing advantages in security, industrial strength, and power-efficient operations.

The power-efficient operating modes are as follows:

- 50 µA/MHz in Active mode

- 124 µA in Deep Sleep mode

- 2.39 µA in Power Down mode

- 1.5 µA in Deep Power Down mode

This application note describes the following contents of MCXN23x:

- · Power domains and power supplies

- Power modes

- Low power entry and configurations

- Wake-up source and wake-up time

- Low power and wake-up optimization

- Demo that reproduces the power consumption and wake-up time specified in the MCX N23x data sheet

# 2 Power domains and power supplies

This section describes the overall power domains, voltage supplies, and different power supply configurations.

#### 2.1 Power domains and voltage supplies

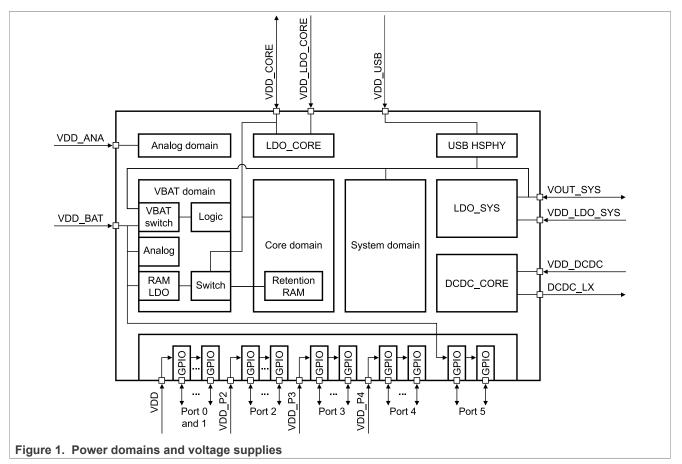

The device contains the following domains: CORE\_MAIN, CORE\_WAKE, CORE\_SRAM, SYSTEM, VBAT, USB, VDD, IO\_2, IO\_3, IO\_4, and ANALOG. Figure 1 shows the overall power domains and voltage supplies. This section mainly introduces the CORE, SYSTEM, and VBAT domains. For specific modules contained in each domain, refer to the "Power domain assignments for modules" table in the *MCX N23x Reference Manual*.

AN14317

#### Low power implementation on MCXN236

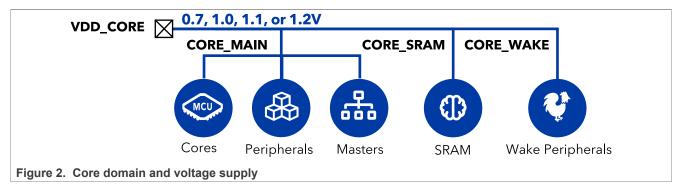

Figure 2 shows the CORE domain supply voltage for most digital modules, and is divided into three subdomains, namely CORE\_MAIN domain, CORE\_SRAM domain, and CORE\_WAKE domain. CORE\_MAIN domain mainly includes cores, peripherals and masters (DMAs, SmartDMA, and so on). The CORE\_SRAM domain includes all RAM blocks. The CORE\_WAKE domain includes wake-up peripherals (Windowed Watchdog Timer, CTIMER0, and so on).

In active mode, VDD\_CORE can be configured to 1.2 V (Over Drive mode), 1.1 V (Standard Drive mode), and 1.0 V (Mid Drive mode). In Power Down mode, VDD\_CORE can be configured to 0.7 V. <u>Table 1</u> describes the maximum frequency that CPU and AHB can achieve at different voltage levels.

#### Table 1. Voltage level and frequency

| VDD_CORE | f <sub>CPU</sub> , f <sub>AHB</sub> ≤ |  |

|----------|---------------------------------------|--|

| 1.2 V    | 150 MHz                               |  |

| VDD_CORE | f <sub>CPU</sub> , f <sub>AHB</sub> ≤ |  |  |  |

|----------|---------------------------------------|--|--|--|

| 1.1 V    | 100 MHz                               |  |  |  |

| 1.0 V    | 50 MHz                                |  |  |  |

| 0.7 V    | Gated off                             |  |  |  |

#### Table 1. Voltage level and frequency...continued

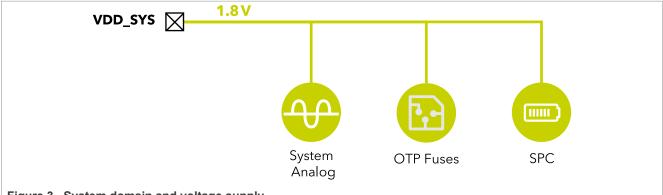

<u>Figure 3</u> shows that the SYSTEM domain is used for power management, including high voltage detect / low voltage detect (HVD / LVD) and system power control (SPC). The normal mode supply voltage of this power domain is 1.8 V. It supports Fuse programming at 2.5 V.

**Note:** The maximum total accumulated time for elevated VDD\_SYS (VDD\_SYS > 1.98 V) is 20 seconds over the lifetime of the device.

Figure 3. System domain and voltage supply

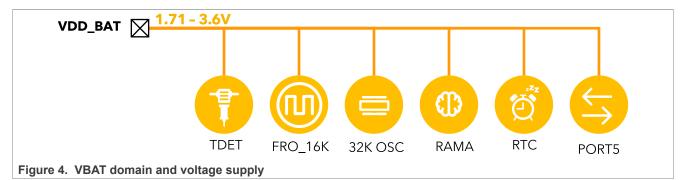

Figure 4 shows the VBAT domain supply to always-ON modules, including OSC\_32K, FRO\_16K, back up retention RAMA regulator, RTC, and PORT5. The VDD BAT ranges from 1.71 V - 3.6 V.

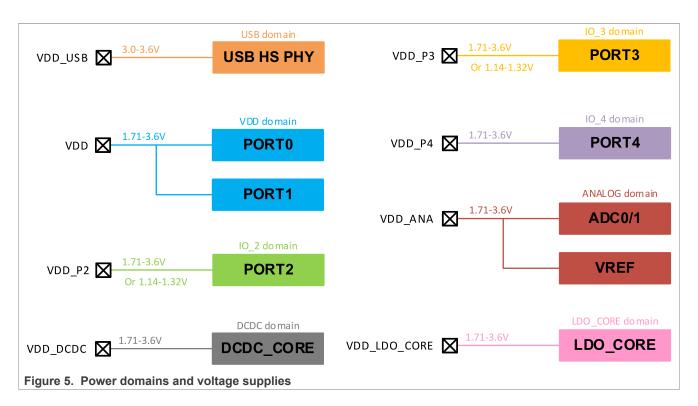

In addition to the power domains already described above, <u>Figure 5</u> shows the remaining power domains of this device, along with the corresponding modules and voltage supply ranges.

# Low power implementation on MCXN236

# 2.2 Power supply configurations

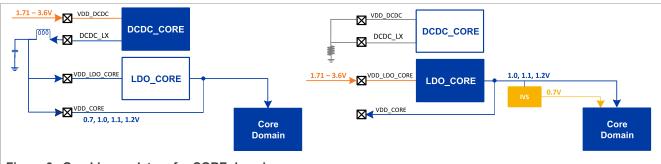

<u>Figure 6</u> shows that the on-chip DCDC converter or LDO regulator is used to regulate the input voltage to the appropriate VDD\_CORE to supply the CORE domain.

When using DCDC\_CORE to generate VDD\_CORE, it has better efficiency than LDO\_CORE. For the device package, which has the VDD\_LDO\_CORE pin, should short this VDD\_LDO\_CORE pin to the VDD\_CORE pin, and disable LDO\_CORE by configuring the CNTRL[CORELDO\_EN] bit field.

Another configuration is to use LDO\_CORE to generate VDD\_CORE to save cost and eliminate the passive components for the DCDC\_CORE. For packages where VDD\_DCDC has an independent pin, you can connect VDD\_DCDC and DCDC\_LX to GND with a 10 k $\Omega$  resistor to disable DCDC. For packages where VDD\_DCDC and VDD\_LDO\_SYS share a package pin, to disable DCDC, DCDC\_LX must be floating. Regardless of the package, you must disable DCDC\_CORE by configuring the CNTRL[DCDC\_EN] bit field.

**Note:** In Power Down mode, DCDC\_CORE can directly output 0.7 V, however, LDO\_CORE must enable Internal Voltage Scaling (IVS) to supply 0.7 V to the CORE domain.

Figure 6. On-chip regulators for CORE domain

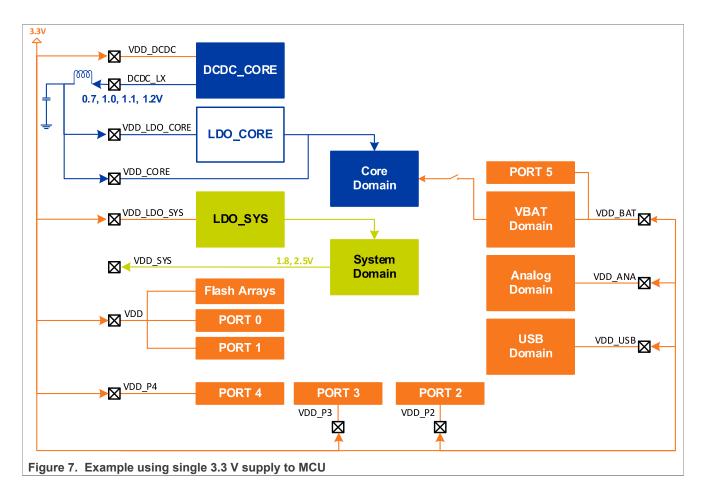

<u>Figure 7</u> shows an example using a single 3.3 V supply to MCU, which uses the power-efficient DCDC\_CORE. It can also be changed to low-cost LDO\_CORE by referring to <u>Figure 6</u>.

#### Low power implementation on MCXN236

# 3 Power modes

The device supports Active, Sleep, Deep Sleep, Power down, Deep Power Down, and VBAT power modes. <u>Table 2</u> describes the status of Clock, CORE\_MAIN domain, CORE\_WAKE domain, SYSTEM domain, FLASH, and SRAM in different power modes. <u>Table 2</u> can be used to compare the status of these modules in different power modes or find the status of these modules in a certain power mode.

| Table 2. | Modules | status | and | power | modes |

|----------|---------|--------|-----|-------|-------|

|----------|---------|--------|-----|-------|-------|

|                | Active    | Sleep     | Deep Sleep              | Power Down            | Deep Power<br>Down | VBAT       |

|----------------|-----------|-----------|-------------------------|-----------------------|--------------------|------------|

| Clock gate off | NO        | Only CPU  | Optional <sup>[1]</sup> | All                   | All                | All        |

| CORE_MAIN      | ON        | ON        | LP <sup>[2]</sup>       | Static <sup>[3]</sup> | OFF <sup>[4]</sup> | OFF        |

| CORE_WAKE      | ON        | ON        | LP                      | LP/Static             | OFF                | OFF        |

| SYSTEM         | ON        | ON        | ON                      | ON                    | ON                 | OFF        |

| Flash          | ON/Static | ON/Static | Static                  | OFF                   | OFF                | OFF        |

| System SRAM    | ON/Static | ON/Static | Static                  | Static/OFF            | OFF                | OFF        |

| VBAT RAMA      | ON/Static | ON/Static | Static                  | Static/OFF            | Static/OFF         | Static/OFF |

[1] Optional means CPU, System, and Bus clock OFF, however, FIRC, SIRC, and SOSC can be enabled by configuring the corresponding STEN bit.

[2] LP means that it can be active with an async functional clock.

[3] Static means that the module is in state retention status (no clock but the data can be kept).

[4] OFF means power down.

© 2024 NXP B.V. All rights reserved.

AN14317

The following sections introduce the features of different power modes.

### 3.1 Active

The default mode after reset.

- Clocks to CPU, memories, and peripherals are enabled.

- CPU execution is possible.

- Adjust VDD\_CORE to the minimum possible value based on the required frequency to achieve optimal power consumption. For details, see <u>Table 1</u>.

### 3.2 Sleep

- CPU clock OFF.

- System and Bus clock remain ON.

- Most modules can remain operational.

- Use the ACTIVE\_CFG register to configure core voltage level and drive strength.

### 3.3 Deep Sleep

- CPU clock, System clock, and Bus clock OFF.

- SRAM is in Deep Sleep mode (SRAM cannot be accessed, however, the data is retained).

- SOSC, SIRC, and FIRC can be enabled by configuring the corresponding STEN bit.

- Some modules can remain operational with low power asynchronous clock sources.

### 3.4 Power Down

It is the lowest power mode that can retain all registers.

- CPU clock, System clock, and Bus clock OFF.

- Flash memory is powered off.

- Place the CORE\_MAIN domain of the chip into a static state.

- The CORE\_WAKE domain can be configured to Deep Sleep or Power Down mode.

- SRAM blocks can be configured to deep sleep or shutdown individually.

- The voltage of the CORE domain can be regulated to 0.7 V (retention voltage).

### 3.5 Deep Power Down

The device wakes from Deep Power Down mode through the Reset routine.

- CPU clock, System clock, and Bus clock OFF.

- Flash memory is powered off.

- The CORE domain is powered off.

- The SYSTEM domain remains ON.

- System RAM is powered off.

- RAMA can be retained.

### 3.6 VBAT

VBAT mode permits the lowest power level. Powering off VDD\_SYS and VDD\_CORE externally puts the chip into VBAT mode.

AN14317 Application note © 2024 NXP B.V. All rights reserved.

- CPU clock, System clock, and Bus clock OFF.

- CORE domain, SYSTEM domain, Flash, and System SRAM are powered off.

- The POR sequence wakes the chip from VBAT mode.

- RAMA can be retained.

# 4 Low power entry and configurations

This section describes the low power mode entry controllers and related configurations in low power mode.

#### 4.1 Low power entry

As described in <u>Table 5</u>, the power mode entered is controlled by CKCTRL[CKMODE] and PMCTRLMAIN[LPMODE] bit fields.

The CKCTRL[CKMODE] bit field configures the amount of clock gating when the core enters a low power mode because of WFI or WFE. <u>Table 3</u> describes the functions corresponding to different CKMODE values. Configuring CKMODE > 0 requires the SLEEPDEEP field in the Arm core to become 1. Configuring PMCTRLMAIN[LPMODE] > 0 requires writing 1111b to CKMODE.

#### Table 3. Function of CKMODE field

| CKCTRL[CKMODE] | Function                                                                        |

|----------------|---------------------------------------------------------------------------------|

| 0000b          | No clock gating                                                                 |

| 0001b          | Core clock gated                                                                |

|                | Core, platform, and peripheral clocks are gated, and core enters low power mode |

The CORE\_MAIN domain and CORE\_WAKE domain have independent registers for configuring low power modes that are PMCTRLMAIN and PMCTRLWAKE. <u>Table 5</u> lists allowed combinations for CORE\_MAIN domain and CORE\_WAKE domain.

PMCTRLMAIN[LPMODE] selects the desired low power mode when a core executes a WFI or WFE instruction. Writes to this field are blocked if you have not enabled the protection level using Power Mode Protection (PMPROT). <u>Table 4</u> describes the functions corresponding to different LPMODE values.

#### Table 4. Function of LPMODE field

| PMCTRLx[LPMODE] | Function        |

|-----------------|-----------------|

| 0000b           | Active/Sleep    |

| 0001b           | Deep Sleep      |

| 0011b           | Power Down      |

| 1111b           | Deep Power Down |

<u>Table 5</u> shows all the configurations of the device to enter low power mode.

#### Table 5. Power mode entry

| Power mode | CKCTRL<br>[CKMODE] | PMPROT<br>[LPMODE] |       | PMCTRLWAKE<br>[LPMODE] |

|------------|--------------------|--------------------|-------|------------------------|

| Active     | N/A                | N/A                | N/A   | N/A                    |

| Sleep      | 0000b              | 0000b              | 0000b | 0000b                  |

|            | 0001b              |                    |       |                        |

© 2024 NXP B.V. All rights reserved

| Power mode      | CKCTRL<br>[CKMODE] | PMPROT<br>[LPMODE] | PMCTRLMAIN<br>[LPMODE] | PMCTRLWAKE<br>[LPMODE] |

|-----------------|--------------------|--------------------|------------------------|------------------------|

| Deep Sleep      | 1111b              | 0001b              | 0001b                  | 0001b                  |

| Power Down      | 1111b              | 0011b              | 0011b                  | 0001b                  |

|                 |                    | 00110              |                        | 0011b                  |

| Deep Power Down | 1111b              | 1111b              | 1111b                  | 1111b                  |

Table 5. Power mode entry...continued

#### Note:

- In Sleep mode, configure CKCTRL[CKMODE] to 0000b for faster wake-up time or 0001b for lower power consumption.

- If more functionality is needed in Power Down mode, leave the CORE\_WAKE domain in Deep Sleep mode.

#### 4.2 Configuration highlights

In addition to selecting power mode, you can also configure relevant hardware in different power modes. The ACTIVE\_CFG and ACTIVE\_CFG1 registers configure the hardware in Active and Sleep mode, such as regulators voltage level and drive strength. Autonomous change to use LP\_CFG and LP\_CFG1 when in low power mode (Deep Sleep, Power Down, and Deep Power Down).

Table 6. Configuration highlights

| ACTIVE_CFG<br>LP_CFG   | Configures:<br>• Regulators voltage level<br>• Regulators drive strength                                                                                                                            |

|------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                        | Enables:<br>• HVDs, LVDs<br>• Bandgap, BG buffer, CMP buffer<br>• VDD_CORE Glitch Detect<br>• VDD voltage detect<br>• Low power current reference IREF<br>• VDD_CORE Internal Voltage Scaling (IVS) |

| ACTIVE_CFG1<br>LP_CFG1 | Enables:<br>• CMPs, CMP DACs, and VREF<br>• USB 3V detect                                                                                                                                           |

# 5 Wake-up

<u>Table 7</u> describes normal wake-up source and typical wake-up time in different low power modes, where the typical wake-up time is the data in the data sheet.

| Symbol              | Description               | Wake-up source    | Typical wake-up time |  |  |

|---------------------|---------------------------|-------------------|----------------------|--|--|

| t <sub>SLEEP</sub>  | Sleep -> Active           | All peripherals   | 0.22 µs              |  |  |

| t <sub>DSLEEP</sub> | Deep Sleep -> Active      | Async peripherals | 8.7 μs               |  |  |

| t <sub>PWDN</sub>   | Power Down -> Active      | WUU, Reset pin    | 9.8 µs               |  |  |

| t <sub>DPWDN</sub>  | Deep Power Down -> Active | WUU, Reset pin    | 5.6 ms               |  |  |

#### Table 7. Wake-up information

# 6 Low power and wake-up optimization

This section explains various methods for optimizing power consumption and factors to consider for wake-up optimization.

#### 6.1 Power consumption optimization

Following are the different ways of performing power consumption optimization.

- Regulator

- Configure the appropriate voltage level and drive strength.

- In Power Down mode, DCDC\_CORE and IVS can provide 0.7 V to the CORE domain. DCDC\_CORE

provides better efficiency and therefore lower power consumption, and IVS reduce wake-up latency with fast

voltage changes.

- Peripherals

- Disable unused analog peripherals by ACTIVE\_CFG1 and LP\_CFG1 registers.

- Memories

- Flash

- Set FLASHDOZE bit when the MCU enters low power mode.

- SRAM

- Manual clock gating by the AHBCLKCTRL0 register of SYSCON.

- Auto clock gating by the AUTOCLKGATEOVERRIDE and AUTOCLKGATEOVERRIDEC registers of SYSCON.

- RAMA is the only block that can be retained in all power modes.

- SYSTEM SRAM can be individually disabled or retained as shown in Table 8.

| SRAMDIS[i] | SRAMRET[i] | MCU Power Mode             | SRAM power mode |  |

|------------|------------|----------------------------|-----------------|--|

| 1b         | N/A        | All                        | Shutdown        |  |

|            | N/A        | Active or Sleep            | Active          |  |

| Ob         |            | Deep Sleep                 | Deep Sleep      |  |

| du         | Ob         | Power Down                 | Deep Sleep      |  |

|            | 1b         |                            | Shutdown        |  |

| N/A        | N/A        | Deep Power Down or<br>VBAT | Shutdown        |  |

#### Table 8. SRAM configurations

#### Note:

- Active of SRAM means you can access SRAM normally.

- Deep Sleep of SRAM means you cannot access SRAM but the data is retained.

- Shutdown of SRAM means you cannot access SRAM and data is lost.

- Clocks

- Select the appropriate CPU clock.

- Disable unused clock source.

- Configure the AHBCLKCTRLx registers of SYSCON to disable or divide the clocks to modules.

- Disable SCG LDO if PLL and SOSC are not used.

- Monitors

- Disable unused voltage monitors.

#### 6.2 Wake-up time consideration

The following are some points to consider with wake-up time:

- SLOW\_CLK frequency

- The wake-up process is implemented through the core mode controller (CMC). SLOW\_CLK is the clock source of CMC and its frequency is equal to ¼ SYSTEM\_CLK.

- Different VDD\_CORE level

- Recovery time required for different voltage levels. For details, refer to the "LPWKUP\_DELAY configuration" table in the MCX N23x Reference Manual.

- The longer time of Clock recovery time and Flash recovery time.

- Interrupt latency

# 7 Demo operation

The following demo is used to reproduce the typical power consumption (see section "*Power consumption operating behaviors*") and wake-up time (see "*Power mode transition operating behaviors*" table) data in the *MCX N23x Data Sheet*. You can also modify its parameters to measure the power consumption and wake-up time corresponding to different configurations.

#### 7.1 Hardware requirement

- FRDM-MCXN236 board Rev. C

- One Type-C USB cable

#### Note:

- To measure wake-up time, the prerequisite is to prepare an oscilloscope or logic analyzer.

- To measure power consumption, the prerequisite is to prepare an MCU-Link Pro or multimeter.

#### 7.2 Software requirement

• IAR 9.50.1

#### 7.3 Setup

This section explains the steps to set up the demo, download and configure the project, and select power mode. It also explains how to measure power consumption and wake-up time.

#### 7.3.1 Hardware setup

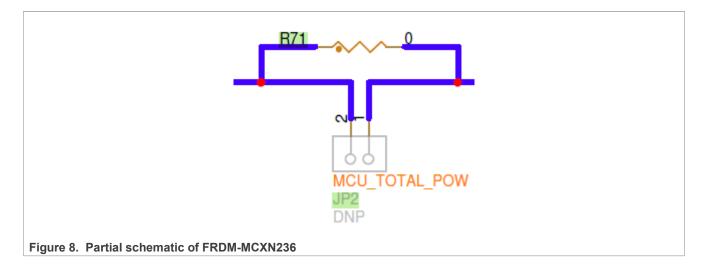

- 1. Remove R71, solder the header at JP2, and use the jumper to connect as shown in Figure 8.

- 2. Use a Type-C USB cable to connect J10 of FRDM-MCXN236 and the USB port of the PC.

Low power implementation on MCXN236

### 7.3.2 Download project

Download the project from the link: <u>https://github.com/nxp-appcodehub/dm-low-power-measurement-on-mcxn236</u> or refer to the associated software file (*AN14317SW*) available on <u>nxp.com</u>.

#### 7.3.3 Configure and download project

As shown in <u>Figure 8</u>, the default configuration for this project is WAKEUP\_EN=0, which is used to reproduce the power consumption data in the data sheet. If you want to reproduce the wake-up time in the data sheet, update it to WAKEUP\_EN=1.

| Category:<br>General Options ^<br>Static Analysis<br>Runtime Checking                                                                                                                                                                                              | Factory Settings     Discard Unused Publics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| C/C++ Compiler<br>Assembler                                                                                                                                                                                                                                        | Language 1         Language 2         Code         Optimizations         Output           List         Preprocessor         Diagnostics         Encodings         Extra Options                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Output Converter<br>Custom Build<br>Linker<br>Build Actions<br>Debugger<br>Simulator<br>CADI<br>CMSIS DAP<br>E2/E2 Lite<br>GDB Server<br>G+LINK<br>I-jet<br>J-Link/J-Trace<br>TI Stellaris<br>Nu-Link<br>PE micro<br>ST-LINK<br>Third-Party Driver<br>TI MSP-FET v | Ignore standard include directories         Additional include directories: (one per line)         \$PROJ_DIR\$/board         \$PROJ_DIR\$/cource         \$PROJ_DIR\$/component/lists         \$CANF_FLOAT_ENABLE=0         \$Preprocessor output to file         \$PROJ_ADVANCED_ENABLE         \$Preserve comments         \$Generate #line directives |

|                                                                                                                                                                                                                                                                    | OK. Cancel                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

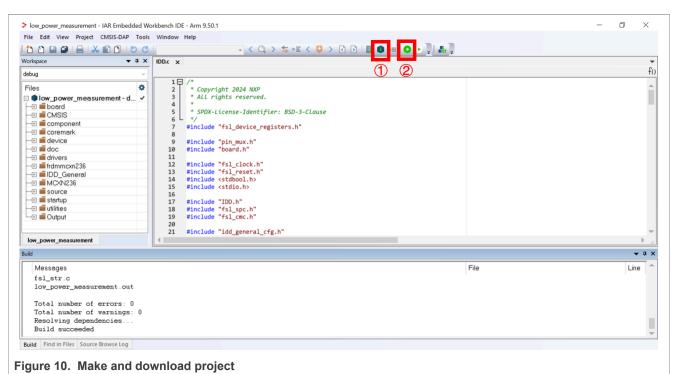

As shown in Figure 10, make and download the project to FRDM-MCXN236.

Low power implementation on MCXN236

### 7.3.4 Select power mode

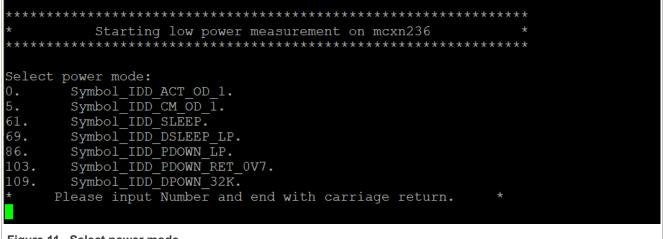

- 1. Open a serial terminal with a 57600 baud rate.

- 2. Follow the prompts in Figure 11 and enter a number to select a different power mode.

#### Figure 11. Select power mode

3. After inputting the case number, the symbol and register values are printed as shown in Figure 12.

Figure 12. Configuration information of different power modes

Low power implementation on MCXN236

|                            | 2           |

|----------------------------|-------------|

| <pre>select_case = 0</pre> |             |

| IDD_ACT_OD_1               |             |

|                            |             |

| Configure 1A.              |             |

| Active Mode Selected       |             |

| Read registers:            |             |

| CMC CKCTRL                 | :0x0        |

| CMC PMPROT                 | :0x0        |

| CMC GPMCTRL                | :0x0        |

| CMC PMCTRLMAIN             | :0x0        |

| CMC PMCTRLWAKE             | :0x0        |

| CMC SRAMDIS0               | :0x0        |

| CMC SRAMRET0               | :0x0        |

| CMC FLASHCR                | :0x0        |

| CMC DBGCTL                 | :0x0        |

| SCG RCCR                   | :0x5000000  |

| SCG SOSCCSR                | :0x1810001  |

| SCG_SOSCCFG                | :0x14       |

| SCG_SIRCCSR                | :0x1800000  |

| SCG FIRCCSR                | :0x800000   |

| SCG FIRCCFG                | :0x0        |

| SCG LDOCSR                 | :0x80000009 |

| SCG APLLCSR                | :0x3000003  |

#### 7.3.5 Measure power consumption

Two ways of measuring power consumption are:

- Using MCU-Link Pro

- Using multimeter

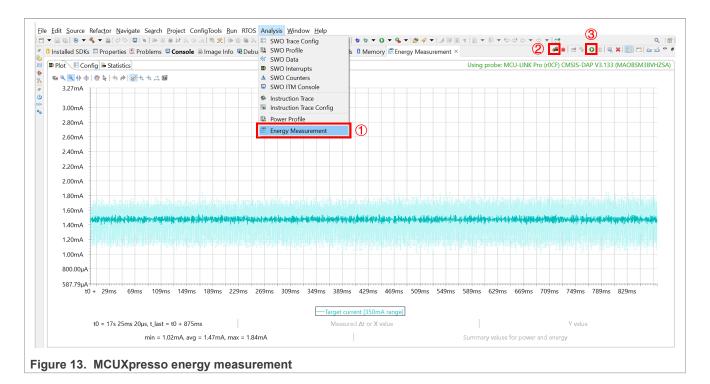

#### 7.3.5.1 Use MCU-Link Pro and MCUXpresso IDE to measure power consumption

1. Connect MCU-Link Pro and FRDM-MCXN236 according to <u>Table 9</u> and afterward connect MCU-Link Pro and FRDM-MCXN236 to the host PC.

#### Table 9. MCU-Link Pro and FRDM-MCXN236 connection

| MCU-Link Pro | FRDM-MCXN236 |

|--------------|--------------|

| J9-1         | JP2-2        |

| J9-3         | JP2-1        |

| J9-2         | J3-14        |

2. Follow the steps shown in Figure 13 to measure current with MCUXpresso.

#### Low power implementation on MCXN236

#### 7.3.5.2 Use a multimeter to measure power consumption

You can also use a multimeter to measure the current at JP2 of the FRDM-MCXN236 board.

#### 7.3.6 Measure wake-up time

As shown in <u>Figure 14</u>, get the wake-up time by measuring the delay between the falling edges of J8-13 (P0\_20) and J8-28 (P3\_11) using an oscilloscope.

#### Low power implementation on MCXN236

| /ertical Digital | Horiz/Acq | Trigger                | Display               | Cursors              | Measure | Math               | Masks                                                                                                          | Save          | Recall       | Help   | •                   | Te                   | k 📃 🖡           |

|------------------|-----------|------------------------|-----------------------|----------------------|---------|--------------------|----------------------------------------------------------------------------------------------------------------|---------------|--------------|--------|---------------------|----------------------|-----------------|

|                  |           |                        |                       |                      |         |                    | the second s | · ! ·         |              |        | · · · · ·           |                      |                 |

|                  |           |                        |                       |                      |         |                    |                                                                                                                |               |              |        |                     |                      |                 |

|                  |           |                        |                       |                      |         | · · · +            |                                                                                                                |               |              |        |                     |                      |                 |

|                  |           |                        |                       |                      |         |                    |                                                                                                                |               |              |        |                     |                      |                 |

|                  |           |                        | P0_2                  | 20                   |         | · · · <del>]</del> |                                                                                                                |               |              |        |                     |                      |                 |

|                  | 50.0      | 194                    |                       | s the                | wake    | un hi              | tton                                                                                                           |               |              |        |                     |                      |                 |

|                  | 00.0      |                        | 1165                  | 5 the                | wane    |                    |                                                                                                                |               |              |        |                     |                      |                 |

|                  |           |                        |                       |                      |         |                    |                                                                                                                |               |              |        |                     |                      |                 |

|                  |           |                        |                       |                      |         |                    |                                                                                                                |               |              |        |                     |                      |                 |

| •                |           | -                      |                       |                      |         | Baud Mentalson     |                                                                                                                |               |              |        |                     |                      |                 |

|                  |           |                        |                       |                      |         | Ţ                  |                                                                                                                |               |              |        |                     |                      |                 |

|                  |           |                        | and the second second |                      |         |                    | -                                                                                                              |               |              |        | · · · · · · ·       |                      |                 |

|                  |           |                        |                       | Wentle out a Walling |         |                    |                                                                                                                | Hall Hale     |              |        |                     |                      |                 |

|                  |           |                        |                       |                      |         | · · · <del>]</del> |                                                                                                                |               |              |        |                     | 22 11                |                 |

|                  |           |                        |                       |                      |         |                    |                                                                                                                |               |              |        |                     | P3_11                |                 |

|                  |           |                        |                       |                      |         | ‡                  |                                                                                                                |               |              |        | 50.0%               | MCU w                | oken u          |

|                  |           |                        |                       |                      |         |                    |                                                                                                                |               |              |        |                     |                      |                 |

|                  |           |                        |                       |                      |         |                    |                                                                                                                |               |              |        |                     |                      |                 |

|                  |           |                        |                       |                      |         | · · · ]            |                                                                                                                |               |              |        |                     |                      |                 |

| •                |           |                        |                       |                      |         |                    |                                                                                                                |               |              |        | advertiged a second |                      |                 |

|                  |           |                        |                       |                      |         | · · · +            |                                                                                                                |               |              |        |                     |                      |                 |

|                  |           |                        |                       |                      |         |                    |                                                                                                                |               |              |        |                     |                      |                 |

|                  |           |                        | <u> </u>              |                      |         | <u> </u>           |                                                                                                                |               |              |        |                     |                      |                 |

| C10 1.0V/div     |           | MO BW:1.0G             |                       |                      |         |                    |                                                                                                                | A' C1<br>None | <b>1.5</b> √ | Normal | 1.0ms/div           | v 10.0MS/s<br>Single | 100ns/pt<br>Sea |

| 000 1.0V/div     | 1         | ΜΩ <sup>B</sup> W:1.0G |                       |                      |         |                    |                                                                                                                | Mone          |              | Normal | 1 acqs              | onigie               | RL:100k         |

|                  | Value     | Mean                   | Min                   | Max                  |         |                    | int Info                                                                                                       |               |              |        | Auto 1              | 月7日,2007             | 06:13:2         |

| C1C2 Dely*       | 5.604ms   | 5.6035069              | m 5.604m              | 5.604m               | 0.0     | 1.0                |                                                                                                                | J             |              |        |                     |                      |                 |

|                  |           |                        |                       |                      |         |                    |                                                                                                                |               |              |        |                     |                      |                 |

Figure 14. Measure wake-up time

### 7.4 Reference results

The power consumption and wake-up time in <u>Table 10</u> are provided as a reference.

### Note:

- Different samples, temperature, and measuring instruments affect test results.

- Before measuring each data, POR is required.

- To measure the power consumption of IDD\_CM\_OD\_1, port CoreMark to this project.

- The wake-up time of Deep Power Down must be configured as 144 MHz boot, and all other measurement data uses the default 48 MHz boot.

- To measure the wake-up time of other configurations, refer to the "LPWKUP\_DELAY configuration" table in the MCX N23x Reference Manual.

- Refer to "Power mode transition operating behaviors" table in MCX N23x data sheet that lists wake-up time, and "Power consumption operating behaviors" section in MCX N23x data sheet that describes different power consumption data.

| Table 10. Test results on the | FRDIVI-IVICAN230 DOALD          | Nev. C                      |                               |                     |

|-------------------------------|---------------------------------|-----------------------------|-------------------------------|---------------------|

| Symbol                        | Power consumption in data sheet | Tested power<br>consumption | Wake-up time in<br>data sheet | Tested wake-up time |

| IDD_ACT_OD_1                  | 7.43 mA                         | 7.679 mA                    | N/A                           | N/A                 |

| IDD_CM_OD_1                   | 8.93 mA                         | 8.763 mA                    | N/A                           | N/A                 |

| IDD_SLEEP                     | 1.48 mA                         | 1.451 mA                    | 0.22 µs                       | 0.22 µs             |

| IDD_DSLEEP_LP                 | 0.12 mA                         | 0.120 mA                    | 8.7 µs                        | 8.6 µs              |

| IDD_PDOWN_LP                  | 1.75 µA                         | 1.95 µA                     | 9.8 µs                        | 9.7 µs              |

| IDD_PDOWN_RET_0V7             | 2.52 µA                         | 2.89 µA                     | N/A                           | N/A                 |

| IDD_DPOWN_32K                 | 1.28 µA                         | 1.55 µA                     | 5.6 ms                        | 5.6 ms              |

Table 10. Test results on the FRDM-MCXN236 board Rev. C

# 8 Summary

This application note introduces the power domains, power modes, low power entry, wake-up, and low power and wake-up optimization of MCXN23x, and provides a demo to reproduce the typical power consumption and wake-up time data in the *MCX N23x data sheet*.

# 9 Note about the source code in the document

The example code shown in this document has the following copyright and BSD-3-Clause license:

Copyright 2024 NXP Redistribution and use in source and binary forms, with or without modification, are permitted provided that the following conditions are met:

- 1. Redistributions of source code must retain the above copyright notice, this list of conditions and the following disclaimer.

- 2. Redistributions in binary form must reproduce the above copyright notice, this list of conditions and the following disclaimer in the documentation and/or other materials provided with the distribution.

- 3. Neither the name of the copyright holder nor the names of its contributors may be used to endorse or promote products derived from this software without specific prior written permission.

THIS SOFTWARE IS PROVIDED BY THE COPYRIGHT HOLDERS AND CONTRIBUTORS "AS IS" AND ANY EXPRESS OR IMPLIED WARRANTIES, INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE ARE DISCLAIMED. IN NO EVENT SHALL THE COPYRIGHT HOLDER OR CONTRIBUTORS BE LIABLE FOR ANY DIRECT, INDIRECT, INCIDENTAL, SPECIAL, EXEMPLARY, OR CONSEQUENTIAL DAMAGES (INCLUDING, BUT NOT LIMITED TO, PROCUREMENT OF SUBSTITUTE GOODS OR SERVICES; LOSS OF USE, DATA, OR PROFITS; OR BUSINESS INTERRUPTION) HOWEVER CAUSED AND ON ANY THEORY OF LIABILITY, WHETHER IN CONTRACT, STRICT LIABILITY, OR TORT (INCLUDING NEGLIGENCE OR OTHERWISE) ARISING IN ANY WAY OUT OF THE USE OF THIS SOFTWARE, EVEN IF ADVISED OF THE POSSIBILITY OF SUCH DAMAGE.

# 10 Revision history

Table 11 summarizes the revisions to this document.

#### Table 11. Revision history

| Document ID | Release date | Description            |

|-------------|--------------|------------------------|

| AN14317 v.1 | 14 May 2024  | Initial public release |

AN14317 Application note

#### Low power implementation on MCXN236

# Legal information

### Definitions

**Draft** — A draft status on a document indicates that the content is still under internal review and subject to formal approval, which may result in modifications or additions. NXP Semiconductors does not give any representations or warranties as to the accuracy or completeness of information included in a draft version of a document and shall have no liability for the consequences of use of such information.

# Disclaimers

Limited warranty and liability — Information in this document is believed to be accurate and reliable. However, NXP Semiconductors does not give any representations or warranties, expressed or implied, as to the accuracy or completeness of such information and shall have no liability for the consequences of use of such information. NXP Semiconductors takes no responsibility for the content in this document if provided by an information source outside of NXP Semiconductors.

In no event shall NXP Semiconductors be liable for any indirect, incidental, punitive, special or consequential damages (including - without limitation lost profits, lost savings, business interruption, costs related to the removal or replacement of any products or rework charges) whether or not such damages are based on tort (including negligence), warranty, breach of contract or any other legal theory.

Notwithstanding any damages that customer might incur for any reason whatsoever, NXP Semiconductors' aggregate and cumulative liability towards customer for the products described herein shall be limited in accordance with the Terms and conditions of commercial sale of NXP Semiconductors.

**Right to make changes** — NXP Semiconductors reserves the right to make changes to information published in this document, including without limitation specifications and product descriptions, at any time and without notice. This document supersedes and replaces all information supplied prior to the publication hereof.

Suitability for use — NXP Semiconductors products are not designed, authorized or warranted to be suitable for use in life support, life-critical or safety-critical systems or equipment, nor in applications where failure or malfunction of an NXP Semiconductors product can reasonably be expected to result in personal injury, death or severe property or environmental damage. NXP Semiconductors and its suppliers accept no liability for inclusion and/or use of NXP Semiconductors products in such equipment or applications and therefore such inclusion and/or use is at the customer's own risk.

**Applications** — Applications that are described herein for any of these products are for illustrative purposes only. NXP Semiconductors makes no representation or warranty that such applications will be suitable for the specified use without further testing or modification.

Customers are responsible for the design and operation of their applications and products using NXP Semiconductors products, and NXP Semiconductors accepts no liability for any assistance with applications or customer product design. It is customer's sole responsibility to determine whether the NXP Semiconductors product is suitable and fit for the customer's applications and products planned, as well as for the planned application and use of customer's third party customer(s). Customers should provide appropriate design and operating safeguards to minimize the risks associated with their applications and products.

NXP Semiconductors does not accept any liability related to any default, damage, costs or problem which is based on any weakness or default in the customer's applications or products, or the application or use by customer's third party customer(s). Customer is responsible for doing all necessary testing for the customer's applications and products using NXP Semiconductors products in order to avoid a default of the applications and the products or of the application or use by customer's third party customer(s). NXP does not accept any liability in this respect.

Terms and conditions of commercial sale — NXP Semiconductors products are sold subject to the general terms and conditions of commercial sale, as published at https://www.nxp.com/profile/terms, unless otherwise agreed in a valid written individual agreement. In case an individual agreement is concluded only the terms and conditions of the respective agreement shall apply. NXP Semiconductors hereby expressly objects to applying the customer's general terms and conditions with regard to the purchase of NXP Semiconductors products by customer.

**Export control** — This document as well as the item(s) described herein may be subject to export control regulations. Export might require a prior authorization from competent authorities.

Suitability for use in non-automotive qualified products — Unless this document expressly states that this specific NXP Semiconductors product is automotive qualified, the product is not suitable for automotive use. It is neither qualified nor tested in accordance with automotive testing or application requirements. NXP Semiconductors accepts no liability for inclusion and/or use of non-automotive qualified products in automotive equipment or applications.

In the event that customer uses the product for design-in and use in automotive applications to automotive specifications and standards, customer (a) shall use the product without NXP Semiconductors' warranty of the product for such automotive applications, use and specifications, and (b) whenever customer uses the product for automotive applications beyond NXP Semiconductors' specifications such use shall be solely at customer's own risk, and (c) customer fully indemnifies NXP Semiconductors for any liability, damages or failed product claims resulting from customer design and use of the product for automotive applications beyond NXP Semiconductors' standard warranty and NXP Semiconductors' product specifications.

**Translations** — A non-English (translated) version of a document, including the legal information in that document, is for reference only. The English version shall prevail in case of any discrepancy between the translated and English versions.

Security — Customer understands that all NXP products may be subject to unidentified vulnerabilities or may support established security standards or specifications with known limitations. Customer is responsible for the design and operation of its applications and products throughout their lifecycles to reduce the effect of these vulnerabilities on customer's applications and products. Customer's responsibility also extends to other open and/or proprietary technologies supported by NXP products for use in customer's applications. NXP accepts no liability for any vulnerability. Customer should regularly check security updates from NXP and follow up appropriately. Customer shall select products with security features that best meet rules, regulations, and standards of the intended application and make the ultimate design decisions regarding its products and is solely responsible for compliance with all legal, regulatory, and security related requirements concerning its products, regardless of any information or support that may be provided by NXP.

NXP has a Product Security Incident Response Team (PSIRT) (reachable at <u>PSIRT@nxp.com</u>) that manages the investigation, reporting, and solution release to security vulnerabilities of NXP products.

$\ensuremath{\mathsf{NXP}}\xspace \mathsf{B.V.}\xspace \longrightarrow \mathsf{NXP}\xspace \mathsf{B.V.}\xspace$  is not an operating company and it does not distribute or sell products.

# Trademarks

Notice: All referenced brands, product names, service names, and trademarks are the property of their respective owners. **NXP** — wordmark and logo are trademarks of NXP B.V.

#### Low power implementation on MCXN236

AMBA, Arm, Arm7, Arm7TDMI, Arm9, Arm11, Artisan, big.LITTLE, Cordio, CoreLink, CoreSight, Cortex, DesignStart, DynamIQ, Jazelle, Keil, Mali, Mbed, Mbed Enabled, NEON, POP, RealView, SecurCore, Socrates, Thumb, TrustZone, ULINK, ULINK2, ULINK-ME, ULINK-PLUS, ULINKpro, µVision, Versatile — are trademarks and/or registered trademarks of Arm Limited (or its subsidiaries or affiliates) in the US and/or elsewhere. The related technology may be protected by any or all of patents, copyrights, designs and trade secrets. All rights reserved. **IAR** — is a trademark of IAR Systems AB. **MCX** — is a trademark of NXP B.V.

# Low power implementation on MCXN236

### Contents

| 1       | Introduction                        | 2  |

|---------|-------------------------------------|----|

| 2       | Power domains and power supplies    | 2  |

| 2.1     | Power domains and voltage supplies  | 2  |

| 2.2     | Power supply configurations         | 5  |

| 3       | Power modes                         | 6  |

| 3.1     | Active                              | 7  |

| 3.2     | Sleep                               | 7  |

| 3.3     | Deep Sleep                          | 7  |

| 3.4     | Power Down                          | 7  |

| 3.5     | Deep Power Down                     | 7  |

| 3.6     | VBAT                                |    |

| 4       | Low power entry and configurations  | 8  |

| 4.1     | Low power entry                     |    |

| 4.2     | Configuration highlights            |    |

| 5       | Wake-up                             |    |

| 6       | Low power and wake-up optimization  |    |

| 6.1     | Power consumption optimization      |    |

| 6.2     | Wake-up time consideration          |    |

| 7       | Demo operation                      |    |

| 7.1     | Hardware requirement                |    |

| 7.2     | Software requirement                |    |

| 7.3     | Setup                               |    |

| 7.3.1   | Hardware setup                      |    |

| 7.3.2   | Download project                    |    |

| 7.3.3   | Configure and download project      |    |

| 7.3.4   | Select power mode                   |    |

| 7.3.5   | Measure power consumption           | 14 |

| 7.3.5.1 | Use MCU-Link Pro and MCUXpresso IDE |    |

|         | to measure power consumption        | 14 |

| 7.3.5.2 | Use a multimeter to measure power   |    |

|         | consumption                         |    |

| 7.3.6   | Measure wake-up time                |    |

| 7.4     | Reference results                   |    |

| 8       | Summary                             | 17 |

| 9       | Note about the source code in the   |    |

|         | document                            |    |

| 10      | Revision history                    |    |

|         | Legal information                   | 18 |

|         |                                     |    |

Please be aware that important notices concerning this document and the product(s) described herein, have been included in section 'Legal information'.

© 2024 NXP B.V.

All rights reserved.

For more information, please visit: https://www.nxp.com

Date of release: 14 May 2024 Document identifier: AN14317