Author

NXP

At NXP, innovation is always now, but our focus is always the future. Our dedicated team of experts is united by a passion to make everyday life more remarkable through technologies that continually redefine life as we know it.

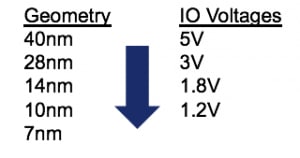

The death of Moore’s law has been rumored for years now. And while it may be slowing down, it’s not done yet. One of the effects of Moore’s law is a shift to lower voltages. As process geometries advance from 40nm to 28nm to 14nm to 10nm and smaller, the voltage levels of both the core and the IO banks continue to move lower. Today’s newest digital ICs, FPGAs, processors, ASICs and microcontrollers, are all pushing for lower voltages.

Figure 1. Process geometry vs IO voltage comparison

One of the benefits of this shift to lower voltages is lower overall power. In the digital domain, bits are still flipping from a 0 to a 1. But the most critical factor when it comes to power and its associated heat generation is whether the “1” is 5V, 3.3V, 1.8V, 1.0V, 0.8V or something else. It takes less energy to switch a transistor from 0V to 1.8V than to switch from 0V to 3.3V. As today’s digital ICs pack millions or billions of transistors in compact footprints on advanced processes, power dissipation and heat have become critical factors. How do you meet your processing and computing needs without blowing the power budget?

Size + Power = Universal Concerns

Die size is another critical factor. In a market full of advanced digital ICs, keeping the die size to a minimum is a necessity for all applications. Whether you’re designing a large communications system, a server motherboard or an edge computing portable sensor, size and power are universal concerns. One way to reduce the die size is to decrease the voltage. Exact ratios will vary over process and other design parameters. But in some cases, dropping the supply voltage to an IO bank can save 5x to 10x or more, in terms of die size. This is why we see today’s newest FPGAs only offering IO voltage banks up to 1.8V, and no longer 3.3V or 5V. The same is quickly becoming true for microcontrollers. Getting a new micro with a 5V IO bank is difficult.

Peripheral Device Voltages Not Dropping as Quickly

But while the digital ICs push the boundaries of Moore’s law, the peripheral devices that surround them in the system are not moving as quickly. Those surrounding devices, often analog or mixed signal, aren’t always in such a rush to get to the newest process node.

Take an analog to digital converter (ADC) for example. For the widest dynamic range, or best signal to noise ratio (SNR), you actually want as large of a voltage as possible. Driving the ADC input with 0 to 5V or the old industrial standard of +/-10V gives you a more accurate reading potential. As ADCs move to lower supply voltages and input voltages, the dynamic range shrinks and it gets more difficult to get a viable reading.

The same is true for other analog and mixed signal peripherals. The need simply isn’t there for moving to the newest process node and the most aggressive (lowest) voltage levels possible. If you have a trusted peripheral you’ve used for multiple generations, there may not be a compelling need to swap it. On the other hand, the newest microcontroller or FPGA may have some features your newest design can’t live without. The catch is that the new microcontroller or FPGA may not have an IO voltage that your existing peripheral can communicate with.

Voltage Level Translator Example Cases

This is where voltage level translators offer a good fit for bridging system gaps. Got a processor that only goes up to 1.8V on its IO banks, but your peripheral operates to 3V minimum on its logic voltage? No problem, use a level translator. Designing an aggressive consumer application and your apps processor wants to communicate from a 1.2V logic voltage to your EEPROM that only ranges down to 1.8V? Again, use a level translator. See Figure 2 for three such examples.

Figure 2. Level Translator Typical Use Case Examples

Conceptually, level translators are fairly easy to understand. There’s an “A” and a “B” side. Each side can have its own supply voltage that sets the logic voltage maximum (or “1,” in digital-speak). In the examples given above, the A side can connect to the digital IC and the B side can connect to the peripheral. This allows the system to communicate across different ICs with different voltage domains. Some of the most common examples for level translators are for digital communication across I2C, SPI, 1-wire or other parallel busses.

When you’re communicating between a processor and a critical sensor or other peripheral, the last thing you want to worry about is the level translator. This is why level translators should be relatively simple, reasonably cost-effective and with robust system performance.

NTS0304 Introduction

NXP offers multiple families of level translators. The newest addition is the NTS0304, a 4-channel device that offers a really wide 0.95V to 5.5V range in an industry standard TSSOP-14 package. The NTS0304 also offers a “smart one shot” to control the slew rate of the output rising edge to ensure very low overshoot for improved ESD and system reliability.

Previous generations of level translators, such as the NTS0104, included higher ringing on the rising edge. An NTS0104 vs NTS0304 comparison is detailed in Figure 3. By controlling the internal slewing, the NTS0304’s smart one shot is able to trade off slightly lower switching speed for improved system robustness.

The NTS0304 is part of an upcoming family of 1, 2, 4 and 8-channel level translators. By operating down to 0.95V, this family is well equipped to handle today’s newest digital ICs, as well as the next generation of low-voltage IO banks.

Conclusion

While the mobile and high-performance data communications systems lead the way with the newest FPGAs, processors, microcontrollers and ASICs, other markets will be quick to follow in the coming years. In all cases, matching the IO voltage bank on your new digital IC to your favorite peripheral devices will often require a level translator. As you survey the market for the right level translator, be sure to consider the right mix of channels, price and system performance.

At NXP, innovation is always now, but our focus is always the future. Our dedicated team of experts is united by a passion to make everyday life more remarkable through technologies that continually redefine life as we know it.